# **BUNDESPATENTGERICHT**

# IM NAMEN DES VOLKES URTEIL

| 2 Ni 25/22     | Verkündet am     |

|----------------|------------------|

| (Aktenzeichen) | 29. Februar 2024 |

In der Patentnichtigkeitssache

. . .

# betreffend das deutsche Patent DE 10 2011 003 843

hat der 2. Senat (Nichtigkeitssenat) des Bundespatentgerichts auf Grund der mündlichen Verhandlung vom 29. Februar 2024 unter Mitwirkung der Vorsitzenden Richterin Hartlieb sowie der Richter Dipl.-Phys. Dr. rer. nat. Friedrich, Dipl.-Phys. Dr. rer. nat. Schwengelbeck, Dr. Himmelmann und Dr.-Ing. Kapels

#### für Recht erkannt:

- Patentanspruch 1 und Patentanspruch 2 des deutschen Patents DE 10 2011 003 843 werden dadurch teilweise für nichtig erklärt, dass Patentanspruch 1 und Patentanspruch 2 dieses Patents folgende Fassung erhalten:

- Halbleitervorrichtung mit einer SiC-Halbleiterschicht (2), einem Wannenbereich (4), der selektiv an einer Oberfläche der SiC-Halbleiterschicht (2) gebildet ist, und einem Dotierungsimplantationsbereich (3), der selektiv an einer Oberfläche des Wannenbereichs (4) gebildet ist, wobei der Dotierungsimplantationsbereich (3) eine Vertiefung aufweist, die in einem Abschnitt von ihm an einer Oberfläche des Dotierungsimplantationsbereichs (3)

gebildet ist und der die Vertiefung aufweisende Abschnitt nicht bis zu einem Ende des Dotierimplantationsbereichs (3) reicht,

wobei ein Abschnitt bis zum Ende des Dotierimplantationsbereichs (3) eine hakenförmig nach oben zu einer Deckfläche der Halbleiterschicht (2) hin gebogene Form hat,

wobei mindestens eine Seitenfläche der Vertiefung eine Gateoxidschicht aufweist, und wobei der Abschnitt mit der hakenförmig nach oben zu der Deckfläche der Halbleiterschicht (2) hin gebogenen Form unterhalb einer Poly-Si-Gateelektrode (8) der Halbleitervorrichtung angeordnet ist, wobei sich die Poly-Si-Gateelektrode (8) bis über den die Vertiefung aufweisenden Abschnitt erstreckt.

- Halbleitervorrichtung gemäß Anspruch 1, bei der eine Endfläche des Dotierungsimplantationsbereichs (3) eine verjüngte Form aufweist.

- II. Im Übrigen wird die Klage abgewiesen.

- III. Die Kosten des Rechtsstreits tragen die Klägerin zu 3/4 und die Beklagte zu 1/4.

- IV. Das Urteil ist gegen Sicherheitsleistung in Höhe von 120 % des jeweils zu vollstreckenden Betrages vorläufig vollstreckbar.

#### **Tatbestand**

Die Beklagte ist Inhaberin des deutschen Patents DE 10 2011 003 843 (Streitpatent), das am 9. Februar 2011 unter Inanspruchnahme der Priorität JP 2010-026062 vom 9. Februar 2010 angemeldet worden ist und das die Bezeichnung "SiC-Halbleitervorrichtung und Verfahren zu ihrer Herstellung" trägt. Der Hinweis auf die Erteilung des Streitpatents wurde am 28. Januar 2021 veröffentlicht.

Das im Umfang der Patentansprüche 1 und 2 angegriffene Streitpatent umfasst den unabhängigen Vorrichtungsanspruch 1, den abhängigen Vorrichtungsanspruch 2, die unabhängigen Verfahrensansprüche 3 bis 5 und 7 sowie die abhängigen Verfahrensansprüche 6 und 8.

Die erteilten Patentansprüche 1 und 2 lauten gemäß DE 10 2011 003 843 B4 (Streitpatentschrift) und im Fall des Patentanspruchs 1 mit hinzugefügter Gliederung:

## Patentanspruch 1:

- 1 Halbleitervorrichtung mit

- 2 einer SiC-Halbleiterschicht (2),

- einem Wannenbereich (4), der selektiv an einer Oberfläche der SiC-Halbleiterschicht (2) gebildet ist, und

- 4 einem Dotierungsimplantationsbereich (3), der selektiv an einer Oberfläche des Wannenbereichs (4) gebildet ist,

- wobei der Dotierungsimplantationsbereich (3) eine Vertiefung aufweist, die in einem Abschnitt von ihm an einer Oberfläche des Dotierungsimplantationsbereichs (3) gebildet ist und

- der die Vertiefung aufweisende Abschnitt nicht bis zu einem Ende des Dotierimplantationsbereichs (3) reicht,

- wobei ein Abschnitt bis zum Ende des Dotierimplantationsbereichs (3) eine hakenförmig nach oben zu einer Deckfläche der Halbleiterschicht (2) hin gebogene Form hat, und

- 8 wobei mindestens eine Seitenfläche der Vertiefung eine Gateoxidschicht aufweist.

### Patentanspruch 2:

Halbleitervorrichtung gemäß Anspruch 1, bei der eine Endfläche des Dotierungsimplantationsbereichs (3) eine verjüngte Form aufweist.

Die Klägerin stützt ihre Klage auf den Nichtigkeitsgrund der mangelnden Patentfähigkeit mit Blick auf fehlende Neuheit und fehlende erfinderische Tätigkeit.

Zur Stützung ihres Vorbringens hat die Klägerin die folgenden Dokumente genannt:

NK1 Verletzungsklageschrift der Beklagten gegen die T...GmbH und die T...SE vom 22. April 2022, der die Klägerin als Nebenintervenientin auf Seiten der Verletzungsbeklagten beigetreten ist (auszugsweise);

NK2 DE 10 2011 003 843 B4 (Streitpatentschrift);

NK3 DE 10 2011 003 843 A1 (Anmeldeschrift);

NK4 JP 2010-026062 (Prioritätsschrift);

NK5 DPMA, Registerauszug zum Aktenzeichen 10 2011 003 843.4, Stand am 15. September 2022 (letzte Aktualisierung in DPMAregister am 21. Dezember 2021);

NK6a JP P2002-270838A;

NK6b Übersetzung der NK6a in die deutsche Sprache;

NK7 US 6,096,607A;

NK8a JP P2009-253072A;

NK8b Übersetzung der NK8a in deutsche Sprache;

NK9 Merkmalsgliederung der Ansprüche 1 und 2 des Streitpatents;

NK10 B. Jayant Baliga, Auszüge aus dem Lehrbuch "Silicon Carbide Power Devices", World Scientific Publishing Co. Pte. Ltd., New Jersey, London, Singapore, Beijing, Shanghai, Hongkong, Taipei, Chennai, 2005, ISBN 981-256-605-8;

NK11 Zhe Chuan Feng and Jian H. Zhao (Editor), Auszüge aus dem Lehrbuch "Optoelectronic Properties of Semiconductors and Superlattices", Volume 20: Silicon Carbide: Materials, Processing, and Devices, New York, London, 2004, ISBN 0-203-59496-7 (Adobe eReader Format), ISBN 1-59169-023-4 (Print Edition);

NK12 Carl-Mikael Zetterling (Editor), Auszüge aus dem Lehrbuch "Process Technology for Silicon Carbide Devices", INSPEC, The Institution of Electrical Engineers, London, United Kingdom, 2002, ISBN 0 85296 998 8;

NK13 Jian Wu, Auszüge aus der Dissertation "Design and Fabrication of 4H-Silicon Carbide MOSFETs", New Brunswick, New Jersey, January 2009, UMI Number: 3350179;

NK14 Online-Lexikon Wikipedia, Artikel: Ionenimplantation, zuletzt bearbeitet am 16. Oktober 2009 um 15:06 Uhr;

NK15 Online-Lexikon Wikipedia, Artikel: Metall-Oxid-Halbleiter-Feldeffekttransistor, zuletzt bearbeitet am 4. Februar 2010 um 07:22 Uhr. Die Klägerin überreicht in der mündlichen Verhandlung vom 29. Februar 2024 dem Senat eine in deutscher Sprache verfasste schriftliche Vollmacht für ihre Prozessbevollmächtigte im Original.

Die Klägerin stellt den Antrag,

das deutsche Patent DE 10 2011 003 843 im Umfang der Ansprüche 1 und 2 teilweise für nichtig zu erklären.

Die Beklagte stellt den Antrag,

die Klage abzuweisen.

hilfsweise

das deutsche Patent DE 10 2011 003 843 unter Klageabweisung im Übrigen insoweit teilweise für nichtig zu erklären, als seine Ansprüche 1 und 2 über die Fassung eines der Hilfsanträge 1 bis 4 vom 2. Januar 2023 – modifiziert mit Schriftsatz vom 12. Juni 2023 - und der Hilfsanträge 5 bis 8 vom 12. Juni 2023 – in dieser Reihenfolge – hinausgehen.

Die Beklagte tritt den Ausführungen der Klägerin in allen wesentlichen Punkten entgegen. Die beanspruchte Lehre sei jedenfalls in der Fassung eines der Hilfsanträge patentfähig.

Zur Stützung ihres Vorbringens hat die Beklagte die folgenden Dokumente vorgelegt:

B1 Schriftsatz der Klägerin an das LG D... vom 30. September 2022

(Klageerwiderung, teilweise geschwärzt);

B2 Beschluss des LG D... vom 10. Oktober 2022

(Geheimhaltungsbeschluss);

B3 Schriftsatz der Klägerin an das LG D...vom 21. November 2022 (Stellungnahme zum Schriftsatz der Beklagten vom 11. November 2022 und vom 17. November 2022);

B4 Maschinenübersetzung der NK6 des Europäischen Patentamts vom 31. Mai 2023;

B5 Übersetzung der NK8 durch die Beklagte.

Anspruch 1 des Hilfsantrags 1 ergibt sich aus dem erteilten Anspruch 1, indem das letzte "und" in Merkmal 7 gestrichen und nach Merkmal 8 das folgende Merkmal 9 angefügt wird:

9 und wobei eine Endfläche des Dotierungsimplantationsbereichs (3) eine verjüngte Form aufweist.

Anspruch 1 des Hilfsantrags 2 hat den im Tenor genannten Wortlaut. Er ergibt sich aus dem erteilten Anspruch 1, indem das letzte "und" in Merkmal 7 gestrichen und nach Merkmal 8 das folgende Merkmal 9' angefügt wird:

9' und wobei der Abschnitt mit der hakenförmig nach oben zu der Deckfläche der Halbleiterschicht (2) hin gebogenen Form unterhalb einer Poly-Si-Gateelektrode (8) der Halbleitervorrichtung angeordnet ist, wobei sich die Poly-Si-Gateelektrode (8) bis über den die Vertiefung aufweisenden Abschnitt erstreckt.

Wegen der weiteren Einzelheiten wird auf den Akteninhalt verwiesen.

## Entscheidungsgründe

Die Klage auf Nichtigerklärung des Streitpatents, mit der der Nichtigkeitsgrund der fehlenden Patentfähigkeit nach § 22 Abs. 1 PatG i. V. m. § 21 Abs. 1 Nr. 1 PatG geltend gemacht wird, ist zulässig.

Die Klage ist insoweit begründet, als das Streitpatent im tenorierten Umfang für nichtig zu erklären ist.

I.

1. Das Streitpatent betrifft eine Halbleitervorrichtung mit einer Siliciumcarbid (SiC)-Halbleiterschicht, einem selektiv an einer Oberfläche der SiC-Halbleiterschicht gebildeten Wannenbereich und einem selektiv an einer Oberfläche des Wannenbereichs gebildeten Dotierungsimplantationsbereich.

SiC-Halbleiterbauelemente eignen sich aufgrund der dreimal höheren Bandlücke und der zehnmal höheren Durchbruchfeldstärke von Siliziumcarbid verglichen mit Silizium nicht nur für höhere Temperaturen als Si-Halbleiterbauelemente, sondern sie ermöglichen auch die Bereitstellung von Leistungshalbleiterbauelementen mit dünneren Driftschichten und höheren Dotierungen und folglich geringerem Widerstand und kleinerer Verlustleistung als Si-Leistungshalbleiter.

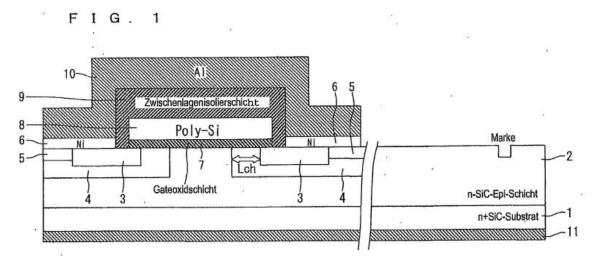

Der Einschaltwiderstand eines SiC-MOSFETs wird maßgeblich durch dessen Kanalwiderstand bestimmt, der wiederum stark von der Kanallänge Lch abhängt, die bei dem in Fig. 1 dargestellten n-Kanal-SiC-MOSFET durch die unter dem Polysilizium-Gate (8) liegende laterale Breite des p-Wannenbereichs (4) zwischen dem n-Sourcebereich (3) und der n-SiC-Epi-Schicht (2) vorgegeben wird.

Wenn die Kanallänge Lch aufgrund einer Fehlausrichtung der beim Bilden des p-Wannen- und des n-Sourcebereichs verwendeten Maske zu stark variiert, kann ein Chip durch lokale Stromkonzentration geschädigt werden, weshalb man bestrebt ist, die Kanallänge Lch der Inversionsschicht präzise einzustellen. Dazu wird nach den Ausführungen in Absatz [0004] des Streitpatents bei einem üblichen Herstellungsverfahren von SiC-MOSFETs zu Beginn des Herstellungsprozesses ein sog. Markenbereich (Marke in Fig. 1) gebildet, der als Referenz für die Maskenausrichtung dient und an dem bspw. die Maskenausrichtung beim Bilden des p-Wannen- und des n-Sourcebereichs ausgerichtet wird. Da gemäß den das Herstellungsverfahren des MOSFETs von Fig. 1 erläuternden Figuren 2 bis 6 und zugehörigen Beschreibung in den Absätzen [0024] bis [0027] die Maskenausrichtung bei den einzelnen Verfahrensschritten jeweils basierend auf dem Markenbereich erfolgt, wird jedoch eine mögliche Maskenfehlausrichtung in jedem Schritt wiederholt, was in Summe eine große Schwankung der Kanallänge Lch bewirken kann. Zudem weist SiC nach den weiteren Ausführungen in den Absätzen [0039] und [0040] aufgrund seines hexagonalen Kristallaufbaus unterschiedliche Oxidationsgeschwindigkeiten in vertikaler und lateraler Richtung auf, was zu deutlichen Dickenänderungen der Gateoxidschicht (7) und infolgedessen zu unerwünschten Schwankungen der Inversionsschicht führen kann.

Vor diesem Hintergrund liegt dem Streitpatent als technisches Problem die Aufgabe zugrunde, einen Aufbau einer Halbleitervorrichtung, der eine Schwankung von Kanallänge und Inversionsschicht unterdrückt, sowie ein Verfahren zu dessen Herstellung bereitzustellen, vgl. Abs. [0006] und [0039] bis [0041].

Gelöst wird diese Aufgabe u. a. durch die Halbleitervorrichtungen der angegriffenen Ansprüche 1 und 2.

Als hier zuständiger Fachmann ist in Übereinstimmung mit den Ausführungen der Klägerin und der Beklagten ein Physiker oder Ingenieur der Fachrichtung Elektrotechnik mit Schwerpunkt Halbleitertechnik und/oder Mikroelektronik zu definieren, der über einen Hochschulabschluss und mehrjährige praktische Erfahrung auf dem technischen Gebiet von Halbleitervorrichtungen verfügt und mit deren Funktionsweise und Herstellung vertraut ist.

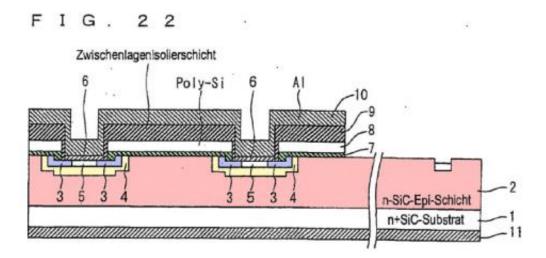

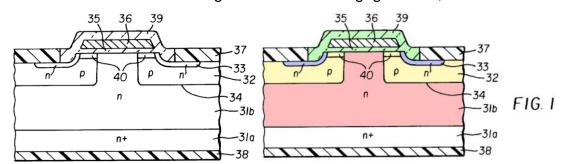

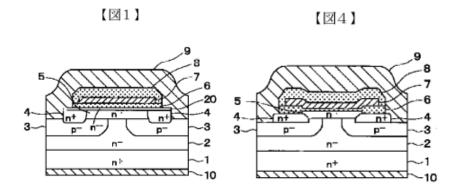

Die beanspruchte Halbleitervorrichtung wird im Streitpatent u. a. anhand der Figuren 22 und 34 erläutert, wobei wegen der besseren Übersichtlichkeit nachfolgend die kolorierte Figur 22 und die kolorierten Ausschnitte der Figuren 22 und 34 aus der Klageschrift vom 16. September 2022 wiedergegeben sind.

#### Merkmale 1 bis 3:

Entsprechend der Darstellung in Figur 22 umfasst die Halbleitervorrichtung eine SiC-Halbleiterschicht (rot kolorierte n-SiC-Epi-Schicht 2), an deren Oberfläche ein Wannenbereich (gelb kolorierter p-Wannenbereich 4), bspw. durch lonenimplantation von Aluminium (Al) oder Bor (B), selektiv gebildet ist.

### Merkmale 4 bis 8:

Zusätzlich ist nach Merkmal 4 an einer Oberfläche des Wannenbereichs (4) durch lonenimplantation von bspw. Stickstoff (N) oder Phosphor (P) selektiv ein Dotierungsimplantationsbereich (violett kolorierter Bereich 3) gebildet, der in den Merkmalen 6 und 7 auch als Dotierimplantationsbereich (3) bezeichnet wird. Beide Begriffe haben inhaltlich die gleiche Bedeutung und umschreiben einen durch lonenimplantation eines Dotierelements gebildeten Bereich. Die weiteren Bezugszeichen 5 bis 11 bezeichnen in obiger Figur 22 den Wannenkontakt (5), die Sourceelektrode (6), die Gateoxidschicht (7), die Polysilizium-Gateelektrode (8), die Zwischenlagenisolierschicht (9), die Aluminiumschicht (10) und die Drainelektrode (11). Somit bildet sich bei einer passenden am Gate (8) anliegenden Spannung ein Inversionskanal im schmalen p-Wannenbereich (4) unterhalb des Gates (8) aus, und der Strom kann von der Sourceelektrode (6) über den Dotierungsimplantationsbzw. Sourcebereich (3) durch den n-Kanal im p-Wannenbereich (4) über die n-SiC-Epi-Schicht (2) und das n<sup>+</sup>-SiC-Substrat zur Drainelektrode (11) fließen. Das in Fig. 22 dargestellte Halbleiterbauelement ist folglich ein vertikaler MOSFET.

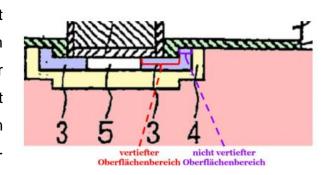

Gemäß den Merkmalen 5 bis 8 weist der Dotierungsimplantationsbereich (3) in Übereinstimmung mit dem der Klageschrift entnommenen Ausschnitt aus Fig. 22 eine Vertiefung auf, die in einem Abschnitt des Dotierungsimplantationsbereichs (3) an einer

Oberfläche des Dotierungsimplantationsbereichs (3) gebildet ist, wobei der die Vertiefung aufweisende Abschnitt nicht bis zu einem Ende Dotierimplantationsbereichs (3) reicht und wobei ein Abschnitt bis zum Ende des Dotierimplantationsbereichs (3) eine hakenförmig nach oben zu einer Deckfläche der Halbleiterschicht (2) hin gebogene Form hat. Zusätzlich weist nach Merkmal 8 mindestens eine Seitenfläche der Vertiefung eine Gateoxidschicht (7, grün koloriert) auf. Durch die Kombination der Merkmale 5 bis 8 wird erreicht, dass der dickere Bereich der Gateoxidschicht (7, grün koloriert) nicht direkt an den p-Wannenbereich (4, gelb koloriert) angrenzt, sondern durch den nach oben gerichteten hakenförmigen Abschnitt des Dotierimplantationsbereichs (3) von ihm beabstandet ist, was eine stabile und nicht schwankende Ausbildung der Inversionsschicht an der Waferoberfläche in der p-Wanne (4) unter dem Gateoxid (7) gewährleistet, vgl. Abs. [0040], [0041] und [0045].

Bei dem in Fig. 22 dargestellten Ausführungsbeispiel ist das Ende des Dotierungsimplantationsbereichs (3) senkrecht nach oben geführt, so dass die gebogene Form im Querschnitt L-förmig ist, vgl. den violett kolorierten Bereich 3, wobei Anspruch 1 nicht auf eine spezielle Form beschränkt ist.

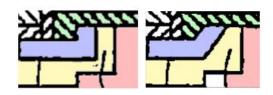

Als Präzisierung enthält Anspruch 1 des Hilfsantrags 1 das Merkmal des erteilten abhängigen Anspruchs 2, wonach eine Endfläche des Dotierungsimplantationsbereichs (3) eine verjüngte Form aufweist. Nach den Figuren 29 bis 40 und der zugehörigen Beschreibung in den Absätzen [0054] bis [0061] versteht das Streitpatent darunter eine schräg nach oben verlaufende Form, wie es auch in

den kolorierten Ausschnitten der Figuren 22 (links) und 34 (rechts) aus dem Klageschriftsatz dargestellt ist. Dabei zeigt der linke Ausschnitt von Fig. 22 die nicht

verjüngte Form des violett kolorierten Dotierungsimplantationsbereichs (3) und der rechte Ausschnitt von Fig. 34 die verjüngte Form.

Mit Hilfsantrag 2 wird die beanspruchte Halbleitervorrichtung dahingehend

präzisiert, dass der Abschnitt mit der hakenförmig nach oben zu der Deckfläche der Halbleiterschicht (2) hin gebogenen Form unterhalb einer Poly-Si-Gateelektrode (8) der Halbleitervorrichtung angeordnet ist, wobei sich die Poly-Si-Gateelektrode (8) bis über den die Vertiefung aufweisenden Abschnitt erstreckt. Entsprechend dem nebenstehenden Ausschnitt aus obiger Figur 22 muss

sich in diesem Fall die Poly-Si-Gateelektrode (8) nicht nur unwesentlich, sondern deutlich bis über den die Vertiefung aufweisenden Abschnitt erstrecken, weshalb eine Poly-Si-Gateelektrode, deren Seitenrand von oben betrachtet mit dem Beginn der Vertiefung zusammenfällt oder sich nur unwesentlich bis über die Vertiefung erstreckt, von dem Merkmal 9' nicht umfasst wird.

Der Begriff Dotier(ungs)implantationsbereich ist erklärungsbedürftig. Er umschreibt entsprechend seinem Wortlaut und in Übereinstimmung mit der Figurenbeschreibung einen durch Ionenimplantation eines Dotierelements gebildeten Bereich. Anspruchsgemäß ist er auf keine spezielle Funktion beschränkt, auch wenn er in den Ausführungsbeispielen der Sourcebereich eines SiC-MOS-Transistors ist (vgl. bspw. Absatz [0046]).

Zum Implantationsschritt an sich ist in Absatz [0038] Folgendes ausgeführt:

"Wenn ein MOSFET unter Verwendung von SiC als Material durch den in Fig. 7-11 gezeigten Vorgang oder den in Fig. 12-16 gezeigten Vorgang gebildet

wird, tritt das folgende Problem auf: in SiC diffundiert ein implantiertes Element anders als bei Si kaum in einer Seitenrichtung. Daher breitet sich der Sourcebereich 3 bei dem in Fig. 8 und Fig. 12 gezeigten Ionenimplantationsschritt von einer Öffnung der Maske 30 aus nicht in einer Seitenrichtung (lateral) aus, sondern ist direkt nach unten gebildet."

Demnach ist bei SiC die Diffusion in Seitenrichtung vernachlässigbar, wobei in dieser Textstelle offengelassen wird, ob dies auch für die Diffusion nach unten gilt. In diesem Zusammenhang belegen aber die das Wissen des Fachmanns dokumentierenden Lehrbuchauszüge NK10 bis NK12, dass in SiC eine relevante Diffusion implantierter Dotier-Ionen generell erst oberhalb von 1800 °C auftritt (vgl. in NK10 die Kapitel 2.3.1 und 2.3.2, in NK11 das Kap. 5.1 und in NK12 die Seiten 51, 74 und 75) und dass solch hohe Temperaturen zu einer Bauelementschädigung führen, weshalb im Herstellungsprozess auf eine nachträgliche Diffusion implantierter Ionen üblicherweise verzichtet wird. Auch die zur Aktivierung der implantierten Ionen notwendige und bspw. in Absatz [0036] des Streitpatents beschriebene Hochtemperaturaktivierungswärmebehandlung erfolgt gemäß den Erläuterungen in obigen Lehrbuchauszügen im Bereich von 1200 bis 1600 °C deutlich unterhalb der jeweiligen Diffusionstemperatur. Ein Hinweis, die dass beanspruchte Halbleitervorrichtung einem Diffusionsprozess unterworfen wird, gibt es im Streitpatent ebenfalls nicht. Zudem weiß der Fachmann, dass Diffusionsprozesse in Festkörpern exponentiell von der Temperatur abhängig und folglich mit obiger Angabe der Diffusions-Grenztemperatur von 1800 °C zum Ausdruck gebracht wird, dass zwar auch bei niedrigen Temperaturen eine geringe Diffusion implantierter lonen auftritt, diese aber aufgrund der exponentiellen Temperaturabhängigkeit erst bei Temperaturen oberhalb von 1800 °C technisch relevant wird. Die Formulierung in Absatz [0038] des Streitpatents, wonach ein implantiertes Element in SiC kaum in einer Seitenrichtung diffundiert und sich daher der Sourcebereich 3 bei dem in Fig. 8 und Fig. 12 gezeigten Ionenimplantationsschritt von einer Öffnung der Maske 30 aus nicht in einer Seitenrichtung ausbreitet, sondern direkt nach unten gebildet

Fachmann somit als Hinweis. versteht der dass der Dotierungsimplantationsbereich bzw. der Sourcebereich (3) ein durch Ionenimplantation eines Dotierelements gebildeter Bereich ist, bei dem der Diffusionsanteil sowohl in lateraler als auch in vertikaler Richtung vernachlässigbar und für die Funktion der Halbleitervorrichtung irrelevant ist. In gleicher Weise ist auch der gemäß Merkmal 7 des Anspruchs 1 hakenförmig nach oben zu einer Deckfläche der Halbleiterschicht gebogene Abschnitt des Dotierungsimplantationsbereichs Ionenimplantation eines Dotierelements gebildeter Bereich.

Demgegenüber hat die Klägerin vorgetragen, dass der Begriff Dotierungsimplantationsbereich breiter ausgelegt werden müsse und von ihm auch relevante Diffusionsbereiche umfasst seien, denn:

- a) der Dotierungsimplantationsbereich werde im Streitpatent mit einem Sourcebereich gleichgesetzt, der üblicherweise einen Diffusionsbereich umfasse,

- b) die im Streitpatent erwähnte Hochtemperaturaktivierungswärmebehandlung werde gemäß NK8, Absatz [0016] in einem Temperaturbereich von 1500 bis 2200 °C durchgeführt, was zu einer Diffusion implantierter Ionen führe,

- c) in gegenständlicher Hinsicht unterscheide sich ein ionenimplantierter Bereich nach einer Hochtemperaturaktivierungswärmebehandlung nicht von einem Diffusionsbereich, da mit der Wärmebehandlung Implantationsschäden entfernt würden (vgl. NK10, Kap. 2.3). Somit beschränke der Begriff Dotierungsimplantationsbereich diesen Bereich auch nicht auf eine Implantation als Dotierungsverfahren, sondern umfasse darüber hinaus diffundierte Dotierungsbereiche.

Dieser Auslegung schließt sich der Senat aus den folgenden Gründen nicht an:

zu a): Anspruch 1 ist auf eine Halbleitervorrichtung mit einem Dotierungsimplantationsbereich gerichtet, ohne dessen Funktion auf einen Sourcebereich zu beschränken. Aus dem Umstand, dass in den Ausführungsbeispielen der Dotierungsimplantationsbereich die Source eines MOS-Transistors ist, kann lediglich abgeleitet werden, dass in den Ausführungsbeispielen die Source des MOS-Transistors ein durch Ionenimplantation eines Dotierelements gebildeter Bereich ist, aber nicht, dass der Dotierungsimplantationsbereich einen Diffusionsbereich umfasst.

zu b) Gemäß dem Lehrbuchauszug NK10 wird die Hochtemperaturaktivierungswärmebehandlung bei Temperaturen im Bereich von 1200 bis 1600 °C durchgeführt, wohingegen SiC oberhalb von 1600 °C aufgrund von Sublimation und Verdampfung geschädigt wird. Diese Schädigung kann man zwar durch spezielle Maßnahmen bei der Wärmebehandlung (vgl. NK10, Kapitel 2.3.2) und durch eine Kohlenstoff-Schutzschicht auf dem SiC abmildern (vgl. NK6, Abs. [0050]), doch gibt es dafür im Streitpatent keinen Hinweis. Wie zudem in obigem Absatz [0038] hervorgehoben wird, breitet sich der "Sourcebereich 3 bei dem in Fig. 8 und Fig. 12 gezeigten Ionenimplantationsschritt von einer Öffnung der Maske 30 aus nicht in einer Seitenrichtung (lateral) aus", d. h. der Sourcebereich wird durch die Ionenimplantation vorgegeben und weder durch die Hochtemperaturaktivierungswärmebehandlung noch durch einen Diffusionsschritt in relevanter Weise vergrößert. Folglich versteht der Fachmann die im Streitpatent beschriebene Hochtemperaturaktivierungswärmebehandlung als Ausheilschritt zur Aktivierung der implantierten Ionen, der entsprechend dem Lehrbuchauszug NK10 bei Temperaturen im Bereich von 1200 bis 1600 °C ohne Schädigung des Halbleitermaterials erfolgt und zu keiner relevanten Diffusion der implantierten lonen führt.

zu c) Entsprechend den von der Klägerin vorgelegten Dokumenten NK10 bis NK14 führt die Ionenimplantation im Kristallgitter des SiC-Halbleiters zu Strahlenschäden, die nachfolgend durch eine Hochtemperaturaktivierungswärmebehandlung reduziert werden. Wird zusätzlich ein Diffusionsprozess zur Vergrößerung des durch Ionenimplantation erzeugten Dotierbereichs durchgeführt, führt dies ausgehend vom Implantationsbereich zu einer Diffusion des Dotierstoffs in

angrenzende Bereiche. Selbst wenn die Wärmebehandlung zu einer vollständigen Beseitigung dieser Schäden führt, hat dieser Diffusionsbereich ein anderes Dotierprofil als der implantierte Bereich. Der durch Ionenimplantation eines Dotierelements erzeugte Dotierungsimplantationsbereich unterscheidet sich folglich auch in gegenständlicher Hinsicht von einem durch Diffusion erzeugten Bereich.

Der Dotierungsimplantationsbereich der beanspruchten Halbleitervorrichtung ist somit dahingehend auszulegen, dass er ein durch Ionenimplantation eines Dotierelements gebildeter Bereich ist, bei dem der Diffusionsanteil sowohl in lateraler als auch in vertikaler Richtung vernachlässigbar und für die Funktion der Halbleitervorrichtung irrelevant ist.

2. Die Halbleitervorrichtungen des erteilten Anspruchs 1 und des Anspruchs 1 nach Hilfsantrag 1 sind bezüglich Druckschrift NK7 nicht neu.

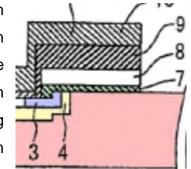

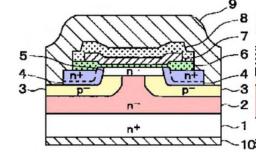

Druckschrift NK7 beschreibt anhand der Fig. 1, die nachfolgend im Original und als kolorierte Variante aus dem Klageschriftsatz wiedergegeben ist,

eine SiC-Halbleitervorrichtung mit einem n<sup>+</sup>-Substrat (31a), einer n-Epitaxialschicht (31b), einem p-Basisbereich (32), einem n-Source-Bereich (33), einem Gate-Isolationsfilm (35), einer Gate-Elektrode (36), einer Source-Elektrode (37), einer Drain-Elektrode (38), einem Zwischenschichtisolierfilm (39) und einem Kanalbereich (40), vgl. Spalte 8, Zeile 30 bis Spalte 10, Zeile 62. In diesen Fundstellen offenbart Druckschrift NK7 mit den Worten des Anspruchs 1 eine

- 1 Halbleitervorrichtung mit

- (vgl. Spalte 1, Zeilen 5 bis 7: "The present invention relates to semiconductor devices having pn junctions, which use silicon carbide as a semiconductor material […].")

- einer SiC-Halbleiterschicht

(n-drift layer 31b / vgl. Spalte 8, Zeilen 45 bis 51 und Spalte 9, Zeilen 21 bis

25, wobei das Bezugszeichen 31a in Zeile 21 ein offensichtlicher

Schreibfehler ist und korrekt 31b heißen muss.),

- einem Wannenbereich (p base regions 32), der selektiv an einer Oberfläche der SiC-Halbleiterschicht (31b) gebildet ist, und

- einem Dotierungsimplantationsbereich *(n source regions 33)*, der selektiv an einer Oberfläche des Wannenbereichs *(32)* gebildet ist,

- wobei der Dotierungsimplantationsbereich (33) eine Vertiefung aufweist (vgl. obige Fig. 1, Bezugszeichen 33 und 34 (recessed portions)), die in einem Abschnitt von ihm an einer Oberfläche des Dotierungsimplantationsbereichs (33) gebildet ist und

- der die Vertiefung aufweisende Abschnitt nicht bis zu einem Ende des Dotierimplantationsbereichs (33) reicht (vgl. obige Fig. 1),

- wobei ein Abschnitt bis zum Ende des Dotierimplantationsbereichs (33) eine hakenförmig nach oben zu einer Deckfläche der Halbleiterschicht (31b) hin gebogene Form hat (vgl. obige Fig. 1), und

- wobei mindestens eine Seitenfläche der Vertiefung eine Gateoxidschicht (gate insulating film 35) aufweist (vgl. obige Fig. 1 und die Figuren 3(d) und 3(e)).

Zwar wird in der Beschreibung der Figuren darauf hingewiesen, dass der Höhenunterschied und damit die Größe der Vertiefung in den Figuren übertrieben dargestellt ist und gemäß Fig. 2(e) möglichst klein sein soll (vgl. den spaltenübergreifenden letzten Satz von Spalte 8 sowie in Spalte 9 die Zeilen 51 bis 63), jedoch ist dort auch angegeben, dass die Vertiefung nach dem Einebnen 0,1 bis 0,2 µm tief ist, was mit der Tiefe übereinstimmt, die die Vertiefung nach der Lehre

des Streitpatents haben soll (vgl. die Absätze [0029] und [0042] des Streitpatents). Daher ist die in Fig. 1 der NK7 dargestellte Vertiefung auch nach dem Verständnis des Streitpatents eine Vertiefung. Dass der Sourcebereich (33) von NK7 eine hakenförmig nach oben zu einer Deckfläche der Halbleiterschicht hin gebogene Form hat, ergibt sich zudem nicht nur aus Fig. 1, sondern auch aus der anhand der Figuren 2(a) bis 2(f) erläuterten Ausbildung der Vertiefung (recessed portions 34), aus der in Spalte 9, Zeilen 51 bis 63 genannten Tiefe nach dem Einebnen (Fig. 2(f)) und aus der Dotierung der Sourcebereiche (33) gemäß Fig. 3(a) und (b).

Das Zusatzmerkmal 9 des Hilfsantrags 1 entnimmt der Fachmann ebenfalls der NK7. Denn wie in Fig. 1 der NK7 gezeigt ist, hat eine Endfläche des Sourcebereichs (33), der dem beanspruchten Dotierungsimplantationsbereich entspricht, eine schräg nach oben verlaufende Form, d. h. eine verjüngte Form, wie sie mit Merkmal 9 beansprucht wird.

Die Halbleitervorrichtungen des erteilten Anspruchs 1 und des Anspruchs 1 nach Hilfsantrag 1 sind somit wegen fehlender Neuheit hinsichtlich Druckschrift NK7 nicht patentfähig.

Bei dieser Sachlage kann dahingestellt bleiben, ob die Druckschriften NK6 und NK8 den Halbleitervorrichtungen des erteilten Anspruchs 1 und des Hilfsantrags 1 patenthindernd entgegenstehen.

- 3. In der aus dem Tenor ersichtlichen Fassung des Hilfsantrags 2 hat das Streitpatent hingegen Bestand.

- 3.1 Die Ansprüche 1 und 2 des Hilfsantrags 2 sind zulässig, denn die Präzisierung 9' in Anspruch 1 des Hilfsantrags 2 ist im Zusammenhang mit dem Gegenstand des erteilten Anspruchs 1 ursprünglich offenbart (vgl. die

ursprünglichen und erteilten Figuren 22, 28, 34 und 40) und der Anspruch 2 des Hilfsantrags 2 entspricht dem ursprünglichen sowie dem erteilten Anspruch 2.

**3.2** Die Halbleitervorrichtung des Anspruchs 1 nach Hilfsantrag 2 ist hinsichtlich Druckschrift NK7 neu und beruht ihr gegenüber auf einer erfinderischen Tätigkeit.

Ausgehend von Druckschrift NK7 gibt es für den Fachmann keine Anregung, die dort in Fig. 1 gezeigte Halbleitervorrichtung und deren Gateelektrode (36) entsprechend dem Zusatzmerkmal 9' des Hilfsantrags 2 so auszugestalten, dass der Abschnitt mit der hakenförmig nach oben zu der Deckfläche der Halbleiterschicht hin gebogenen Form unterhalb einer Poly-Si-Gateelektrode der Halbleitervorrichtung angeordnet ist, wobei sich die Poly-Si-Gateelektrode bis über den die Vertiefung aufweisenden Abschnitt erstreckt.

Zwar ist dieses Merkmal dem Fachmann aus Fig. 7 (d) von Druckschrift NK7 bekannt, doch bezieht sich diese Figur auf eine Ausführungsform, die sich in mehrfacher Hinsicht von der in Fig. 1 gezeigten unterscheidet, da bei ihr die Sourcebereiche (72) keine Dotierungsimplantationsbereiche, sondern epitaktisch aufgewachsene Bereiche sind, und die im Unterschied zu Merkmal 8 wegen der zusätzlichen Epitaxieschicht (71c) keine Seitenfläche der Vertiefung eine Gateoxidschicht aufweist. Aufgrund dieser Unterschiede hat der Fachmann keine Veranlassung, bei der in Fig. 1 gezeigten Ausführungsform die Gateelektrode entsprechend Fig. 7 (d) abzuändern (vgl. BGH, Urteil vom 21. Juli 2022, X ZR 82/20 – Leuchtdiode – zweiter Leitsatz, juris).

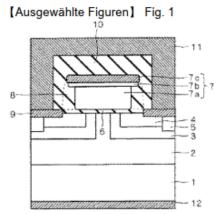

3.3 Die Halbleitervorrichtung des Anspruchs 1 nach Hilfsantrag 2 ist hinsichtlich Druckschrift NK8 neu und beruht ihr gegenüber auf einer erfinderischen Tätigkeit. Druckschrift NK8, auf deren deutsche Übersetzung NK8b im Folgenden Bezug genommen wird, beschreibt in Figur 1 mit Bezugszeichenliste in den Worten des Anspruchs 1 eine

- 1 Halbleitervorrichtung mit (vgl. den Titel: "Halbleiterbauelement und Herstellungsverfahren dafür")

- 2 einer SiC-Halbleiterschicht (Kristallwachstumsschicht 2 / vgl. die Zusammenfassung, Seite 1: "Das erfindungsgemäße Halbleiterbauelement ist ausgestattet mit dem aus Siliziumkarbid bestehenden Halbleitersubstrat 1, an dessen

1 Halbleitersubstrat, 2 epitaktischen Kristallwachstumsschicht, 3 Wannenbereich, 4 Source-Bereich, 5 Wannen-Kontaktbereich, 6 Gate-Oxidfilm, 7 Gate-Elektrode, 7a Siliziumschicht, 7b Siliziumkarbidschicht, 7c, 9 Silizidschicht, 8 Abstandshalter aus thermischem Oxidationsfilm

Oberfläche die epitaktische Kristallwachstumsschicht 2 ausgebildet ist, und mit dem über der epitaktischen Kristallwachstumsschicht 2 selektiv ausgebildeten Wannenbereich 3."),

- 3 einem Wannenbereich (Wannenbereich 3), der selektiv an einer Oberfläche der SiC-Halbleiterschicht (2) gebildet ist, und

- einem Dotierungsimplantationsbereich (Source-Bereich 4), der selektiv an einer Oberfläche des Wannenbereichs (3) gebildet ist.

Patentinhaberin darin zuzustimmen, dass NK8 Kristallwachstumsschicht (2) nicht explizit als SiC-Schicht bezeichnet wird, doch entnimmt der Fachmann dies trotzdem der NK8, denn in Absatz [0011] wird das dort beschriebene Halbleiterbauelement als vertikales MOSFET-Siliziumkarbid-Halbleiterbauelement bezeichnet und gemäß Absatz [0013] wird die epitaktische Kristallwachstumsschicht (2) auf der Oberfläche eines Siliziumkarbid-Halbleitersubstrats (1) ausgebildet. Die Bezeichnung als SiC-MOSFET bedeutet, dass sich der leitende Kanal in einer SiC-Halbleiterschicht ausbildet und folglich die Kristallwachstumsschicht (2) eine SiC-Schicht ist. Auch macht der Einsatz eines relativ teuren SiC-Substrats als Wachstumssubstrat für die Kristallwachstumsschicht (2) nur dann Sinn, wenn die Kristallwachstumsschicht (2) eine SiC-Schicht ist.

Aus der Beschreibung in Absatz [0023] und der zugehörigen Figur 6 geht hervor, dass die Dicke des auf dem SiC-Source-Bereich (4) und nicht unter der Gateelektrode (7) liegenden Teils des Gateoxidfilms (6) bei einem zusätzlichen Oxidationsschritt zur Bildung des thermischen Oxidationsfilms (8) nach oben und unten etwas

zunimmt, weil neben dem Silizium (7a) und dem Siliziumcarbid (7b) auch ein Teil des Gateoxids (6) auf dem SiC-Source-Bereich (4) oxidiert. Dadurch bildet sich eine Vertiefung im SiC-Source-Bereich (4) und eine hakenförmig nach oben zu einer Deckfläche der Kristallwachstumsschicht (2) hin gebogenen Form des Source-Bereichs (4) aus. Dieser Dickenzuwachs auf SiC ist zwar klein und liegt nach Fig. 7 im Bereich von 10 bis 20 nm, weshalb die in Fig. 6 gezeigte Dickenänderung der Gateoxidschicht (6) in den übrigen Figuren der NK8 nicht dargestellt ist, doch werden von Anspruch 1 auch Vertiefungen in diesem Tiefenbereich umfasst, da er diesbezüglich nicht beschränkt ist. Somit offenbart NK8 auch die übrigen Merkmale 5 bis 8 des Anspruchs 1:

- wobei der Dotierungsimplantationsbereich (4) eine Vertiefung aufweist (vgl. Fig. 6, d1), die in einem Abschnitt von ihm an einer Oberfläche des Dotierungsimplantationsbereichs (4) gebildet ist und

- der die Vertiefung aufweisende Abschnitt nicht bis zu einem Ende des Dotierimplantationsbereichs (4) reicht (vgl. Fig. 6),

- wobei ein Abschnitt bis zum Ende des Dotierimplantationsbereichs (4) eine hakenförmig nach oben zu einer Deckfläche der Halbleiterschicht (31b) hin gebogene Form hat (vgl. Fig. 6), und

- wobei mindestens eine Seitenfläche der Vertiefung eine Gateoxidschicht (Gate-Oxidfilm 6) aufweist (vgl. Fig. 6).

Gemäß den Ausführungen in Absatz [0018] der NK8 beinhaltet die Gateelektrode (7) des in den Figuren 1 und 6 beschriebenen MOSFETs eine untere Polysiliziumschicht (7a) und eine obere Siliziumkarbidschicht (7b), deren oberster Teil nach Abscheiden eines Metallfilms (13, Fig. 8) und anschließender Silizidierung (Fig. 9) zusätzlich eine Silizidschicht (7c, Fig. 1) aufweist. Da das Zusatzmerkmal 9' des Hilfsantrags 2 verlangt, dass der Abschnitt mit der hakenförmig nach oben zu der Deckfläche der Halbleiterschicht hin gebogenen Form unterhalb einer Poly-Si-Gateelektrode der Halbleitervorrichtung angeordnet ist, und sich die Poly-Si-Gateelektrode bis über den die Vertiefung aufweisenden Abschnitt erstreckt, ist bei der Beurteilung der Patentfähigkeit bezüglich NK8 die laterale Ausdehnung der Polysiliziumschicht (7a) gegenüber der Vertiefung relevant.

Der in NK8 anhand der Figuren 2 bis 9 erläuterte Herstellungsprozess umfasst, wie in Fig. 6 und Abs. [0023] beschrieben, das thermische Oxidieren der die Polysilizium- und SiC-Schicht (7a, 7b) aufweisenden und auf der Gateoxidschicht (6) angeordneten Gateelektrode (7), wodurch neben der Vertiefung im SiC-Source-Bereich (4) die Oxid-Spacer (8) ausgebildet werden, die wegen der unterschiedlichen Oxidationsraten von Silizium und Siliziumcarbid in der Dicke variieren und entlang der Siliziumseitenflächen wenigstens zehnmal so dick sind (d3) wie entlang der SiC-Seitenflächen (d2). Die starke Oxidation des Polysiliziums (7a) und die gleichzeitige Oxidation der Gateoxidschicht (6) führen im unteren Kantenbereich des Gates zu einer Abrundung der Gateelektrode (7) und zu einer lokalen Verdickung des Spacers (8) im Bereich der Kante (vgl. den gestrichelten Kreis in Fig. 6), was nach den Erläuterungen in Absatz [0023] die Zuverlässigkeit des Transistors erhöht, weil dadurch Kurzschlüsse zwischen der Gateelektrode (7) und dem Sourcebereich (4) aufgrund der nachfolgenden Silizidierung verhindert und das Auftreten elektrischer Feldspitzen im unteren Kantenbereich der Gateelektrode (7) unterbunden werden.

Aus dem Herstellungsprozess ergibt sich, dass die Seitenfläche bzw. die untere Kante der Polysiliziumschicht (7a) den Rand der Vertiefung bestimmt und die laterale Grenze der Vertiefung durch die untere Kante der Polysiliziumschicht (7a) der Gateelektrode (7) vorgegeben wird. Daher ist der Teil des Zusatzmerkmals 9', dass sich die Poly-Si-Gateelektrode bis über den die Vertiefung aufweisenden Abschnitt erstreckt, in NK8 nicht offenbart und durch NK8 auch nicht nahegelegt.

Soweit die Klägerin vorgetragen hat, dass NK8 das Zusatzmerkmal 9' des Hilfsantrags 2 offenbare, weil sich die Polysiliziumschicht (7a) in Fig. 6 der NK8 zumindest in geringem Maße bis über den die Vertiefung aufweisenden Abschnitt erstrecke, teilt der Senat diese Auffassung nicht. Denn mit der Darstellung in Fig. 6 der NK8 kommt zum Ausdruck, dass sich die Polysiliziumschicht (7a) nicht oder nur unwesentlich bis über den die Vertiefung aufweisenden Abschnitt erstreckt, denn die durch die Oxidation des Gateoxids (6) hervorgerufene Vertiefung bildet sich in dem von der Polysiliziumschicht (7a) nicht überdeckten Bereich aus, so dass ihr Rand durch den Seitenrand der Polysiliziumschicht (7a) vorgegeben wird und sich die Polysiliziumschicht (7a) nicht wesentlich über die Vertiefung erstreckt.

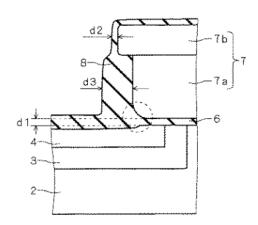

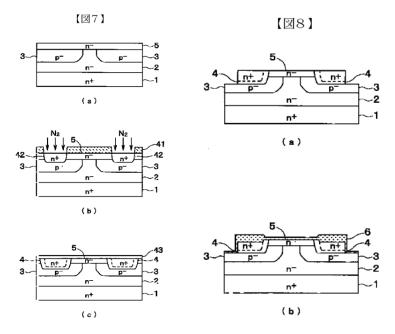

**3.4** Druckschrift NK6, auf deren deutsche Übersetzung NK6b im Folgenden Bezug genommen wird, steht der beanspruchten Halbleitervorrichtung nicht patenthindernd entgegen.

Nach den Ausführungen den Absätzen [0006] bis [0011] in Beschreibungseinleitung von NK6 führt die aufgrund von Ionenimplantation verursachte beschleunigte Oxidation ionenimplantierter Dotierungsbereiche in SiC zu erhöhten Schichtwiderständen und daraus resultierenden verschlechterten Bauelementeigenschaften. Dies soll gemäß den Ausführungen in den Absätzen [0025] bis [0045] entsprechend den Figuren 1 und 4 durch eine auf der Oberseite des ionenimplantierten n<sup>+</sup>-Source-Bereichs (4) und der Oberflächenkanalschicht (5) epitaktisch aufgewachsene n<sup>--</sup>-Epitaxialschicht (20) verhindert werden, die durch einen nachfolgenden thermischen Oxidationsschritt teilweise (Fig. 1) oder vollständig (Fig. 4) zu einem Gate-Oxidfilm (6) umgewandelt wird, der gleichmäßig dick und flach verläuft (Abs. [0035] und Fig. 1) oder zumindest so ausgebildet ist, dass der Schichtwiderstand in der Kontaktzone zwischen dem n<sup>+</sup>-Source-Bereich (4) und der Oberflächenkanalschicht (5) gering ist (vgl. Abs. [0044] und Fig. 4).

Obige Figuren zeigen jeweils eine SiC-Halbleitervorrichtung mit einem n<sup>+</sup>-Substrat (1), einer n<sup>-</sup>-Epitaxialschicht (2), einem p-Basisbereich (3), einem n<sup>+</sup>-Sourcebereich (4), einer n<sup>-</sup>-Oberflächenkanalschicht (5), einem aus der n<sup>-</sup>-Epitaxialschicht (20) gebildeten Gate-Oxidfilm (6), einer Gate-Elektrode (7), einem Zwischenschichtisolierfilm (8), einer Source-Elektrode (9) und einer Drain-Elektrode (10) (vgl. die Bezugszeichenliste auf Seite 34, letzter Absatz). Der schräg verlaufende Randabschnitt der n<sup>+</sup>-Sourcebereiche in Fig. 4 wird durch eine Schrägimplantation der Source-Ionen erreicht, wohingegen die Ionen bei der Vorrichtung in Fig. 1 senkrecht implantiert werden. Eine dritte Variante wird in den

Absätzen [0046] bis [0052] anhand von Fig. 6 erläutert, die als kolorierte Variante aus dem Klageschriftsatz wiedergegeben ist, wobei deren Bezugszeichen mit denen der Figuren 1 und 4 übereinstimmen. Bei dieser Ausgestaltung ist wesentlich, dass - wie in den

Figuren 7(a) bis (c) sowie 8(a) und (b) gezeigt - zunächst Ionen in Source-Teilbereiche (42) implantiert werden (vgl. Fig. 7(b)) und dann nach Aufbringen einer C-Deckschicht (43) eine Wärmebehandlung bei 1900°C durchgeführt wird, um den Source-Bereich in seitlicher Richtung und nach unten zu vergrößern (vgl. Fig. 7(c)).

Der Übergang zwischen dem inneren ionenimplantierten Sourcebereich und dem äußeren Diffusionsbereich ist in obigen Figuren durch eine gestrichelte Linie im Sourcebereich (4) dargestellt. Mit diesem zusätzlichen Diffusionsschritt wird erreicht, dass bei der thermischen Oxidation zur Ausbildung des Gateoxids (6) der ionenimplantierte Teil des Sourcebereichs zwar eine beschleunigte Oxidation erfährt und eine dicke Oxidschicht bildet, aber gleichzeitig der durch Diffusion gebildete Teil des Sourcebereichs normal und in gleicher geringer Dicke wie die angrenzende n°-Oberflächenkanalschicht (5) oxidiert, wodurch der Schichtwiderstand zwischen dem Sourcebereich (4) und der Oberflächenkanalschicht (5) reduziert wird.

Der Sourcebereich (4) des in Fig. 6 dargestellten Transistors hat somit zwar ähnlich wie die beanspruchte Vorrichtung eine hakenförmig nach oben gebogene Form, doch ist dieser hakenförmig ausgebildete Teil des Sourcebereichs (4) im Unterschied zu Merkmal 7 des Anspruchs 1 kein Dotierimplantationsbereich, sondern ein Diffusionsbereich, weshalb die Halbleitervorrichtung des Anspruchs 1 neu gegenüber der in NK6 beschriebenen Vorrichtung ist.

Ausgehend von NK6 gibt es für den Fachmann keinen Anlass, statt der Diffusionsbehandlung eine Ionenimplantation durchzuführen, weil dies zu einer unerwünschten beschleunigten Oxidation auch in dem an die Oberflächenkanalschicht (5) angrenzenden Teil des Sourcegebiets (4) führen würde, was mit der Diffusionsbehandlung gerade verhindert werden soll. Zudem hätte ein Ersetzen der Diffusionsbehandlung durch eine Ionenimplantation zur Folge, dass die Oberseite des Sourcegebiets (4) nicht nur im inneren Bereich, sondern auch in dem an die Oberflächenkanalschicht (5) angrenzenden Teil des Sourcegebiets (4) beschleunigt oxidieren würde und im Unterschied zu Merkmal 7 des Anspruchs 1 keine hakenförmig nach oben gebogene Form mehr hätte, weil sich die Oxidschicht gleichmäßig ausbilden würde.

Die Halbleitervorrichtung des Anspruchs 1 nach Hilfsantrag 2 ist demnach neu hinsichtlich Druckschrift NK6 und beruht ihr gegenüber auf einer erfinderischen Tätigkeit.

3.5 Da auch eine Zusammenschau der Druckschriften NK6 bis NK8 die Halbleitervorrichtung des Anspruchs 1 nach Hilfsantrag 2 nicht nahelegen kann, war die Klage insoweit teilweise abzuweisen. Bei diesem Sachstand bedarf es daher keiner Entscheidung mehr, ob das Streitpatent auch in den Fassungen der Hilfsanträge 3 bis 8 schutzfähig wäre.

II.

Die Kostenentscheidung beruht auf § 84 Abs. 2 Satz 1 und Satz 2 Halbsatz 1 PatG i. V. m. § 92 ZPO.

Die Entscheidung über die vorläufige Vollstreckbarkeit beruht auf § 99 Abs. 1 PatG i. V. m. § 709 Satz 1 und 2 ZPO.

- 28 -

III.

## Rechtsmittelbelehrung

Gegen dieses Urteil ist das Rechtsmittel der Berufung gemäß § 110 PatG statthaft.

Die Berufung ist innerhalb eines Monats nach Zustellung des in vollständiger Form abgefassten Urteils spätestens nach Ablauf von fünf Monaten nach Verkündung durch einen in der Bundesrepublik Deutschland zugelassenen Rechtsanwalt oder Patentanwalt schriftlich oder in elektronischer Form beim Bundesgerichtshof, Herrenstraße 45a, 76133 Karlsruhe, einzulegen.

## Die Berufungsschrift muss

- die Bezeichnung des Urteils, gegen das die Berufung gerichtet ist, sowie

- die Erklärung, dass gegen dieses Urteil Berufung eingelegt werde,

enthalten.

Mit der Berufungsschrift soll eine Ausfertigung oder beglaubigte Abschrift des angefochtenen Urteils vorgelegt werden.

Hartlieb Dr. Friedrich Dr. Schwengelbeck Dr. Himmelmann Dr. Kapels