23 W (pat) 5/20

(Aktenzeichen)

Verkündet am 30. Juni 2020

. . .

# **BESCHLUSS**

## In der Beschwerdesache

## betreffend die Patentanmeldung 10 2013 022 598.1

. . .

hat der 23. Senat (Technischer Beschwerdesenat) des Bundespatentgerichts auf die mündliche Verhandlung vom 30. Juni 2020 unter Mitwirkung des Vorsitzenden Richters Dr. Strößner sowie der Richter Dr. Zebisch, Dr. Himmelmann und Dr. Kapels

#### beschlossen:

- Der Beschluss der Prüfungsstelle für Klasse H01L des Deutschen Patent- und Markenamts vom 20. Dezember 2019 wird aufgehoben.

- 2. Es wird ein Patent erteilt mit der Bezeichnung "Halbleiterbauelement", dem Anmeldetag 26. November 2013 unter Inanspruchnahme der Priorität US 13/685,283 vom 26. November 2012 auf der Grundlage folgender Unterlagen:

- Patentansprüche 1 bis 13,

- Beschreibungsseiten 1 bis 3, 8, 14 und 19, jeweils überreicht in der mündlichen Verhandlung am 30. Juni 2020:

- Beschreibungsseiten 4 bis 7, 9 bis 13, 15 bis 18, 20 und 21,

- 6 Blatt Zeichnungen mit Figuren 1 bis 3, 4A bis 4J, 5A und 5B, jeweils eingegangen im Deutschen Patent- und Markenamt am 23. Oktober 2019.

#### Gründe

I.

Die vorliegende Patentanmeldung mit dem Aktenzeichen 10 2013 022 598.1 und der Bezeichnung "Halbleiterbauelement" wurde am 24. Juli 2019 von der Anmeldung 10 2013 224 134.8 abgeteilt. Die Stammanmeldung wurde am 26. November 2013 unter Inanspruchnahme der US-amerikanischen Priorität …in englischer Sprache angemeldet. Gleichzeitig mit der Anmeldung wurde Prüfungsantrag gestellt. Am 25. Februar 2014 wurde eine deutsche Übersetzung

- 3 -

der ursprünglichen Unterlagen der Stammanmeldung eingereicht, die am 28. Mai 2014 mit der DE 10 2013 224 134 A1 veröffentlicht wurde.

Die Prüfungsstelle für Klasse H01L hat im Prüfungsverfahren der Stammanmeldung auf den Stand der Technik gemäß folgender Druckschriften verwiesen:

D1 US 2007/0 114 602 A1;

D2 US 5 998 836 A.

Sie hat die Teilanmeldung 10 2013 022 598.1 ohne vorherigen Bescheid mit Beschluss vom 20. Dezember 2019 unter Verweis auf den Erstbescheid der Stammanmeldung zurückgewiesen, da der Gegenstand des Anspruchs 1 wörtlich dem der Ansprüche 1, 2 und 3 der Stammanmeldung entspreche, zu dem der Anmelderin bereits im Erstbescheid der Stammanmeldung mitgeteilt worden sei, dass er gegenüber der Lehre der Druckschrift D1 nicht neu und damit nicht patentfähig sei (§ 3 PatG i. V. m. § 1 Abs. 1 PatG). Der Beschluss wurde der Anmelderin am 27. Dezember 2019 elektronisch zugestellt.

Gegen diesen Beschluss hat die Anmelderin mit Schriftsatz vom 27. Januar 2020, am selben Tag elektronisch im Deutschen Patent- und Markenamt eingegangen, Beschwerde eingelegt, die sie mit diesem Schriftsatz auch begründet hat.

In der mündlichen Verhandlung am 30. Juni 2020 hat die Anmelderin einen neuen Satz Patentansprüche und Beschreibungsseiten 1 bis 3, 8, 14 und 19 eingereicht und beantragt:

1. den Beschluss der Prüfungsstelle für Klasse H01L des Deutschen Patentund Markenamts vom 20. Dezember 2019 aufzuheben.

- 2. Ein Patent zu erteilen mit der Bezeichnung "Halbleiterbauelement", dem Anmeldetag 26. November 2013 unter Inanspruchnahme der Priorität …auf der Grundlage folgender Unterlagen:

- Patentansprüche 1 bis 13,

- Beschreibungsseiten 1 bis 3, 8, 14 und 19, jeweils überreicht in der mündlichen Verhandlung am 30. Juni 2020;

- Beschreibungsseiten 4 bis 7, 9 bis 13, 15 bis 18, 20 und 21,

- 6 Blatt Zeichnungen mit Figuren 1 bis 3, 4A bis 4J, 5A und 5B, jeweils eingegangen im Deutschen Patent- und Markenamt am 23. Oktober 2019.

Der in der mündlichen Verhandlung eingereichte Anspruch 1 lautet mit bei unverändertem Wortlaut eingefügter, an die Gliederung des Zurückweisungsbeschlusses angelehnter Gliederung:

- "1. Halbleiterbauelement,

- 1.1 das einen Halbleiterkörper (100) und wenigstens zwei Bauelementzellen, die in dem Halbleiterkörper integriert sind, aufweist, wobei jede Bauelementzelle aufweist:

- 1.2 ein Driftgebiet (11),

- 1.3 ein Sourcegebiet (12) und ein

- 1.4 Bodygebiet (13), das zwischen dem Sourcegebiet (12) und dem Driftgebiet (11) angeordnet ist;

- 1.5 ein Diodengebiet (30) und

- 1.6 einen pn-Übergang zwischen dem Diodengebiet (30) und dem Driftgebiet (11);

- 1.7 einen Graben (110) mit einer ersten Seitenwand (110<sub>1</sub>), einer zweiten Seitenwand (110<sub>2</sub>) gegenüber der ersten Seitenwand (110<sub>1</sub>) und einem Boden (110<sub>3</sub>),

- 1.8 wobei das Bodygebiet (13) an die erste Seitenwand (110<sub>1</sub>) angrenzt, das Diodengebiet (30) an die zweite Seitenwand (110<sub>2</sub>) angrenzt und

- der pn-Übergang an den Boden (1103) des Grabens angrenzt;

- 1.9 eine Gateelektrode (21), die in dem Graben (110) angeordnet ist und die durch ein Gatedielektrikum (22) gegenüber dem Bodygebiet (13), dem Diodengebiet (30) und dem Driftgebiet (11) isoliert ist; und

- 1.10 eine Sourceelektrode (41), die an das Sourcegebiet (12) und das Diodengebiet (30) jeder Bauelementzelle elektrisch angeschlossen ist,

- 1.11 wobei die Diodengebiete (30) der wenigstens zwei Bauelementzellen in einer lateralen Richtung des Halbleiterkörpers (100) beabstandet sind und jeweils aufweisen:

- 1.11.1 ein erstes Diodengebiet (31), das zumindest einen Teil des pn-Übergangs mit dem Driftgebiet (11) bildet und

- 1.11.2 an den Graben (110) ausschließlich am Boden (110<sub>3</sub>) angrenzt; und

- 1.11.3 ein zweites Diodengebiet (32), das höher dotiert ist als das erste Diodengebiet (31),

- 1.11.4 wobei das zweite Diodengebiet (32) ein unteres Ende aufweist und mit einem oberen Ende an die Sourceelektrode (41) angeschlossen ist,

- 1.11.5 wobei das erste Diodengebiet (31) das untere Ende des zweiten Diodengebiets (32) lateral umschließt."

Der auf ein Herstellungsverfahren gerichtete selbständige Anspruch 9 dieses Antrags lautet mit bei unverändertem Wortlaut eingefügter Gliederung:

- "9. Verfahren zum Herstellen eines Halbleiterbauelements, wobei das Verfahren aufweist:

- 9.1 Bereitstellen eines Halbleiterkörpers,

- 9.1.1 der eine Driftgebietschicht (111),

- 9.1.2 eine Bodygebietschicht (113), die an die Driftgebietschicht (111) angrenzt, und

- 9.1.3 eine Sourcegebietschicht (112), die an die Bodygebietschicht (113) angrenzt und die eine erste Oberfläche (101) des Halbleiterkörpers (100) bildet, aufweist;

- 9.2 Herstellen von wenigstens zwei Diodengebieten (30) derart,

- 9.2.1 dass sich jedes Diodengebiet (30) von der ersten Oberfläche (101) durch die Sourcegebietschicht (112) und die Bodygebietschicht (113) in die Driftgebietschicht erstreckt,

- 9.2.2 dass jedes Diodengebiet (30) und die Driftgebietschicht (111) einen pn-Übergang bilden und

- 9.2.3 dass jedes Diodengebiet (30)

- 9.2.3.1 ein erstes Diodengebiet (31), das zumindest einen Teil des pn-Übergangs mit dem Driftgebiet (11) bildet, und

- 9.2.3.2 ein zweites Diodengebiet (32), das höher dotiert ist als das erste Diodengebiet (31), aufweist;

- 9.3 Herstellen von wenigstens zwei Gräben (110), die jeweils eine erste Seitenwand (110<sub>1</sub>) und eine zweite Seitenwand (110<sub>2</sub>) gegenüber der ersten Seitenwand (110<sub>1</sub>) und einen Boden (110<sub>3</sub>) aufweisen, derart,

- 9.3.1 dass jeder Graben (110) an die Bodygebietschicht (113) an einer Seitenwand,

- 9.3.2 ein Diodengebiet (30) an der zweiten Seitenwand und

- 9.3.3 einen pn-Übergang am Boden (110<sub>3</sub>) angrenzt,

- 9.3.4 wobei das erste Diodengebiet (31) an den Graben (110) ausschließlich am Boden (110<sub>3</sub>) angrenzt,

- 9.3.5 wobei das zweite Diodengebiet (32) ein unteres Ende aufweist und wobei das erste Diodengebiet (31) das untere Ende des zweiten Diodengebiets (32) lateral umschließt;

- 9.4 Herstellen einer Gateelektrode (21) und eines Gatedielektrikums (22), das die Gateelektrode (21) dielektrisch gegenüber dem Halbleiterkörper (100) isoliert, in jedem Graben (110);

- 9.5 Herstellen einer Isolationsschicht (51) auf der ersten Oberfläche (101);

- 9.6 Herstellen einer ersten Kontaktöffnung (52) in der Isolationsschicht (51) oberhalb jedes Diodengebiets (30) und jedes Sourcegebiets (12); und

- 9.7 Herstellen einer Sourceelektrode (41), die elektrisch an das Sourcegebiet (12) und ein oberes Ende des zweiten Diodengebiets (32) angeschlossen ist, in jeder ersten Kontaktöffnung (52),

- 9.8 wobei Abschnitte der Sourcegebietschicht (112), die nach dem Herstellen der Diodengebiete (30) verbleiben, die Sourcegebiete (12) bilden, und

- 9.9 wobei Abschnitte der Bodygebietschicht (113), die nach dem Herstellen der Diodengebiete (30) verbleiben, die Bodygebiete (13) bilden.

Hinsichtlich der auf den Anspruch 1 rückbezogenen Unteransprüche 2 bis 8 und der auf Anspruch 9 rückbezogenen Unteransprüche 10 bis 13 sowie der weiteren Unterlagen und Einzelheiten wird auf den Akteninhalt verwiesen.

II.

Die form- und fristgerecht erhobene Beschwerde der Anmelderin ist zulässig und erweist sich hinsichtlich des in der mündlichen Verhandlung am 30. Juni 2020 eingereichten Anspruchssatzes auch als begründet, so dass der Beschluss der Prüfungsstelle für Klasse H01L aufzuheben ist, denn die Ansprüche des in der mündlichen Verhandlung eingereichten Anspruchssatzes sind zulässig (§ 38 PatG), und sowohl das mit dem Anspruch 1 beanspruchte Halbleiterbauelement als auch das mit Anspruch 9 beanspruchte Verfahren zum Herstellen eines solchen sind durch den ermittelten Stand der Technik nicht patenthindernd getroffen, so dass sie patentfähig sind (§§ 1 bis 5 PatG).

**1.** Die Anmeldung betrifft ein Halbleiterbauelement, das ein vertikales Transistorbauelement und eine parallel zu dem Transistorbauelement geschaltete Diode aufweist.

Leistungstransistoren sind Transistoren mit hohen Sperrspannungen von bis zu einigen hundert Volt und mit einer hohen Strombelastbarkeit. Sie können als vertikale MOS-Grabentransistoren (engl.: Vertical MOS Trench Transistors) ausgebildet sein. In diesem Fall ist die Gateelektrode des Transistors in einem Graben ausgebildet, der sich in einer vertikalen Richtung des Halbleiterkörpers erstreckt. Die Gateelektrode ist dielektrisch gegenüber dem Source-, Body- und Driftgebiet des Transistors isoliert und ist in einer lateralen Richtung des Halbleiterkörpers benachbart zu dem Bodygebiet angeordnet. Ein Draingebiet grenzt üblicherweise an das Driftgebiet an, und eine Sourceelektrode ist an das Sourcegebiet angeschlossen.

Bei vielen Anwendungen ist es wünschenswert, dass eine Diode parallel zu der Laststrecke (Drain-Source-Strecke) des Transistors geschaltet ist. Eine integrierte Bodydiode des Transistors kann für diese Zwecke verwendet werden. Die Bodydiode wird durch den pn-Übergang zwischen dem Bodygebiet und dem Driftgebiet gebildet. Um die Bodydiode parallel zu der Laststrecke des Transistors zu schalten, kann das Bodygebiet einfach elektrisch an die Sourceelektrode angeschlossen werden. Allerdings kann die Bodydiode eine Stromtragfähigkeit aufweisen, die bei einigen Anwendungen niedriger als gewünscht ist.

Leistungstransistoren können mit herkömmlichen Halbleitermaterialien realisiert werden, wie beispielsweise Silizium (Si) oder Siliziumkarbid (SiC). Aufgrund der spezifischen Eigenschaften von SiC ermöglicht die Verwendung von SiC die Realisierung von Leistungstransistoren mit einer höheren Spannungsfestigkeit (bei einem gegebenen Einschaltwiderstand) als Si. Allerdings führen hohe Sperrspannungen zu hohen elektrischen Feldern in dem Halbleiterkörper, insbesondere an dem pn-Übergang zwischen dem Bodygebiet und dem Driftgebiet. Üblicherweise gibt es Abschnitte der Gateelektrode und des Gatedielektrikums, die nahe zu diesem pn-Übergang angeordnet sind. Probleme können auftreten, wenn die Spannungsfestigkeit Gatedielektrikums für des eine gewünschte Spannungsfestigkeit des Transistorbauelements nicht ausreichend ist. In diesem Fall kann das Gatedielektrikum vorzeitig durchbrechen (vgl. Seite 1, 1. Abs. bis Seiten 1, 2 seitenübergreifender Abs. der geltenden Beschreibung).

Ausgehend vom diesem geschilderten Stand der Technik liegt der Anmeldung als technisches Problem die Aufgabe zugrunde, ein Halbleiterbauelement mit einem Transistorbauelement und einer Diode zur Verfügung zu stellen, bei dem eine Gateelektrode des Transistors gegenüber hohen elektrischen Feldern geschützt ist, und bei dem die Diode eine hohe Strombelastbarkeit (engl.: high current rating) und niedrige Verluste aufweist, sowie ein Verfahren zum Herstellen eines solchen Halbleiterbauelements zur Verfügung zu stellen (vgl. Seiten 2, 3 seitenübergreifender Abs. der geltenden Beschreibung).

Diese Aufgabe wird durch das Halbleiterbauelement nach dem geltenden Anspruch 1 und das Verfahren zum Herstellen eines Halbleiterbauelements nach Anspruch 9 gelöst.

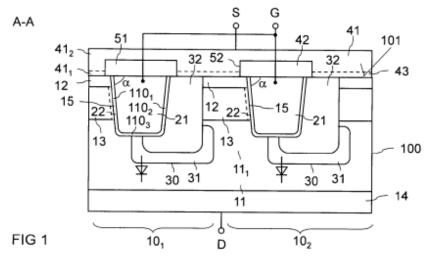

Die Anmeldung zeigt in ihrer hier wiedergegebenen Fig. 1 einen Schnitt durch ein Bauelement gemäß Anspruch 1. Der Halbleiterkörper besitzt von seiner Oberfläche (101) zu seiner Unterseite folgende grundlegende Gebietsfolge: Sourcegebiet (12), Bodygebiet (13) und Driftgebiet (11). Ein Draingebiet (14) wird im Anspruch 1 nicht erwähnt, kann aber nach dem Driftgebiet (11) angeordnet sein. Anspruch 1 macht keine Angaben über die Leitungstypen der einzelnen Gebiete, jedoch müssen für einen funktionierenden senkrecht angeordneten MOSFET das Sourcegebiet (12) und das Driftgebiet (11) vom ersten Leitungstyp und das Bodygebiet (13) vom zweiten Leitungstyp sein.

In diesen Halbleiterkörper mit dieser Gebietsfolge sind mehrere Gräben (110) eingebracht, die zwei gegenüberliegende Seiten (1101, 1102) und einen Boden (1103) aufweisen. Die Seiten (1101, 1102) und der Boden (1103) des Grabens sind mit einem Dielektrikum (22) bedeckt, das auch als Gatedielektrikum wirkt, denn die Gräben sind mit der Gateelektrode (21) aufgefüllt. Es entsteht so auf der ersten Seite (1101) des Grabens der senkrechte MOS-Transistor. Auf der anderen Seite wird dies verhindert, da dort die parallelgeschaltete Diode ausgebildet wird. Diese Diode besteht aus dem Diodengebiet (30), das zwei Teilgebiete (31, 32) umfasst. Dabei ist das erste Dioden(teil)gebiet (31) niedriger dotiert als das zweite Dioden(teil)gebiet (32). Da das Diodengebiet (30) im Driftgebiet einen pn-Übergang ausbildet, muss es von einem anderen Leitungstyp als das Driftgebiet und damit vom selben Leitungstyp wie das Bodygebiet, also vom zweiten Leitungstyp sein. Dieser pn-Übergang grenzt an den Boden des Grabens an.

Fig. 1, die gemäß Beschreibung ein Ausführungsbeispiel darstellt (*vgl. Seite 4, 1. Abs. der geltenden Beschreibung*), zeigt, dass der pn-Übergang zum Driftgebiet (*11*) nicht vom ersten Dioden(teil)gebiet (*31*) allein, sondern auch vom zweiten Dioden(teil)gebiet (*32*) gebildet wird, das bis in den Driftbereich (*11*) hineinreicht, so dass das erste Diodengebiet (*31*) nur einen Teil des pn-Übergangs mit dem Driftgebiet (*11*) bildet. Das erste Diodengebiet (*31*) grenzt an den Graben (*110*) an, und zwar ausschließlich an dessen Boden (*110*<sub>3</sub>), und umschließt das untere Ende des zweiten Diodengebiets (*32*) lateral. Auf diese Weise bildet das niedriger dotierte

erste Diodengebiet (31) den pn-Übergang auch dort aus, wo dieser auf den Boden (1103) des Grabens (110) trifft. Außerdem schließt es durchgängig das Diodengebiet (30)

nach unten ab. Dies hat den Vorteil, dass bei einer Polung des Diodengebiets (30) in Sperrrichtung eine breitere Raumladungszone entsteht, über die die Spannung abfällt, als wenn das höher dotierte Diodengebiet (32) den pn-Übergang ausbilden würde, was zu einem verringerten elektrischen Feld und damit zu einer Verringerung der Durchbruchswahrscheinlichkeit des Materials, insbesondere des Dielektrikums (22) im Graben (110) führt. Unterstützt wird dies durch die Anordnung des pn-Übergangs derart, dass dieser nicht auf die Seitenwände, sondern auf den Boden (1103) des Grabens trifft.

Die Sourceelektrode (41) ist mit den Sourcegebieten (12) aller Zellen und den Diodengebieten (30) aller Zellen elektrisch verbunden, der Driftbereich (11) mit dem Draingebiet (14) oder direkt mit der Drainelektrode.

Wird nun eine Spannung derart angelegt, dass die Dioden in Durchlassrichtung geschaltet sind, so fließt von der Sourceelektrode (41) über die Diodengebiete (30) zum Driftgebiet (11) ein Strom. Die parallelen MOSFETs werden dabei kurzgeschlossen und sind somit wirkungslos. Die Spannung an den Gateelektroden (21) hat keinerlei Einfluss auf den fließenden Strom. Das höher dotierte zweite Diodengebiet (32) garantiert dabei, dass ein hoher Strom auf Grund der hohen Leitfähigkeit des Diodengebiets (30) getragen werden kann.

Wird dagegen eine Spannung angelegt, die zu den Dioden in Sperrrichtung gepolt ist, so breitet sich eine Verarmungszone um den pn-Übergang herum aus und ein Stromfluss über die Diodengebiete (30) wird verhindert. Nun ist der MOSFET wirksam und der Stromfluss kann durch die Spannung an den Gateelektroden (21) gesteuert werden. Diese kann nun so gewählt werden, dass ein Stromfluss über den MOSFET erfolgt. In der Folge ist die Spannung zwischen der Sourceelektrode und der Drainelektrode relativ gering. Dies bedeutet auch, dass die Spannung am pn-Übergang der Diode gering ist und die Verarmungszone relativ dünn ist.

Die Spannung an der Gateelektrode (21) kann auch so gewählt werden, dass auch der MOSFET sperrt. Dann liegt zwischen der Source- und der Drainelektrode die gesamte Spannung an, bei der das Bauelement betrieben wird. Diese würde am MOSFET im Bereich des pn-Übergangs zwischen dem Driftgebiet (11) und dem Bodygebiet (13) abfallen, also über eine relativ kurze Strecke, so dass dort hohe elektrische Felder entstehen. Dem wirkt die besondere Ausbildung des Diodengebiets (30) entgegen. Beim pn-Übergang dehnt sich das Verarmungsgebiet immer weiter aus, solange, bis es mit dem Verarmungsgebiet des pn-Übergangs der benachbarten Zelle überlappt. Es entsteht somit eine über die gesamte Fläche des Bauelements ausgedehnte Verarmungszone, so dass die Spannung über eine deutlich längere Strecke abfällt, was das elektrische Feld verringert und einen Durchschlag verhindert. Die Diodengebiete (30) benachbarter Zellen bilden somit auch noch einen JFET, der den MOSFET schützt (vgl. Seite 7, 1. Abs. bis Seite 12, 2. Abs. der geltenden Beschreibung).

2. Die mit den Ansprüchen beanspruchten Gegenstände und Verfahren sind in der Stammanmeldung ursprünglich offenbart, so dass die Ansprüche zulässig sind (§ 38 PatG).

So geht Anspruch 1 aus dem ursprünglichen Anspruch 1 (Merkmale 1, 1.1 bis 1.9, 1.11) durch Aufnahme der Merkmale der ursprünglichen Ansprüche 2 (Merkmal 1.10) und 3 (Teile des Merkmals 1.11.1, Merkmal 1.11.3 und Teile des Merkmals 1.11.4) hervor. Zudem wurden aus der ursprünglichen Figur 1 weitere Merkmale bezüglich der beiden Diodengebiete (31, 32), die wesentlich für die Wirkungsweise des Halbleiterbauelements sind, in den Anspruch 1 aufgenommen (Teile des Merkmals 1.11.1, Merkmal 1.11.2, Teile des Merkmals 1.11.4, Merkmal 1.11.5). Der mit Anspruch 1 beanspruchte Gegenstand ist somit ursprünglich offenbart und damit Anspruch 1 auch zulässig.

Der selbständige Anspruch 9 geht aus dem ursprünglichen Anspruch 11 (Merkmale 9, 9.1, 9.1.1 bis 9.1.3, 9.2, 9.2.1, 9.2.2, 9.3, 9.3.1 bis 9.3.3, 9.4, 9.8 und 9.9) hervor,

indem in ihn die Merkmale der Ansprüche 12 (Merkmale 9.5, 9.6 und Teile des Merkmals 9.7) und 3 (Merkmal 9.2.3, Teile des Merkmals 9.2.3.1, Merkmal 9.2.3.2) aufgenommen wurden. Hinzu kommen wiederum die aus der ursprünglichen Fig. 1 bereits in Anspruch 1 aufgenommenen Merkmale (Teile des Merkmals 9.2.3.1, Merkmale 9.3.4 und 9.3.5 sowie Teile des Merkmals 9.7). Der ursprüngliche Anspruch 3 bezieht sich zwar nicht auf den ursprünglichen Anspruch 11, sondern über den ursprünglichen Anspruch 2 auf Anspruch 1 zurück, doch ist die Aufnahme seiner Merkmale in den ursprünglichen Anspruch 11 zulässig, denn die in den Fig. 4 und 5 gezeigten Herstellungsverfahren weisen die dem ursprünglichen Anspruch 3 zu entnehmenden Merkmale ebenfalls auf. Damit ist auch das mit Anspruch 9 beanspruchte Verfahren ursprünglich offenbart, so dass Anspruch 9 zulässig ist.

Die Unteransprüche 2 bis 8 und 10 bis 13 gehen aus den ursprünglichen Ansprüchen 4 bis 10 und 13 bis 16 hervor, wobei in den Ansprüchen 12 und 13 berichtigt wurde, dass das Halbleiterbauelement nicht nur einen Graben, sondern eine Mehrzahl von Gräben aufweist, weshalb dort an Stelle des Singulars der Plural gesetzt wurde. Auch die Gegenstände und Verfahren der Unteransprüche sind somit ursprünglich offenbart und damit zulässig.

3. Die Lehren der Ansprüche sind für den Fachmann auch ausführbar (§ 34 Abs. 4 PatG), da bereits ihr Wortlaut mit den Zeichnungen ausreichend ist, um dem Fachmann eine nacharbeitbare Lehre anzugeben. Zudem wird ein Ausführungsbeispiel in Zusammenhang mit den Figuren näher beschrieben.

Als zuständiger Fachmann zur Beurteilung der Erfindung ist hier ein berufserfahrener Physiker oder Ingenieur der Fachrichtung Elektrotechnik mit Hochschul- oder Fachhochschulabschluss zu definieren, der mit der Entwicklung und Verbesserung von Leistungshalbleiterbauelementen betraut ist.

**4.** Der gewerblich anwendbare (§ 5 PatG) Gegenstand des geltenden Anspruchs 1 und das gewerblich anwendbare Verfahren des Anspruchs 9 sind gegenüber dem

ermittelten Stand der Technik neu (§ 3 PatG) und beruhen diesem gegenüber auf einer erfinderischen Tätigkeit (§ 4 PatG) des Fachmanns, so dass sie patentfähig sind (§ 1 Abs. 1 PatG).

**4.1.** Die Zurückweisung der Anmeldung erfolgte auf Grund der fehlenden Neuheit gegenüber der Druckschrift D1. Diese offenbart ein Halbleiterbauelement, das eine Grabengatestruktur aufweist, die als "superjunction structure" bezeichnet wird (*vgl. Abs. [0003]: "This invention relates to a semiconductor device, and more particularly to a semiconductor device of the trench gate structure based on the superjunction structure."*). Eine solche Struktur weist abwechselnd n und p-Säulenregionen auf, die im Driftgebiet vergraben sind. Während des Ausschaltens breiten sich bei einer solchen Struktur die Verarmungszonen lateral aus und führen so zu einer hohen Durchbruchspannung. Im angeschalteten Zustand sorgen die hochdotierten n-Säulen dafür, dass ein hoher Strom fließen kann (*vgl. Abs. [0006]: "Vertical MOSFETs* to solve this problem include those of the superjunction structure. Instead of the n-type layer in the conventional structure, the superjunction structure has p-pillar regions and n-pillar regions alternately buried in the drift layer portion. By

equalizing the amount of impurities contained in the ppillar region and the n-pillar region, the drift layer is artificially made a non-doped layer. During off-time. а horizontally spreading depletion layer high breakdown maintains voltage. During the on-time, a current is allowed to flow through the n-pillar region doped with high concentration. Thus, the superjunction structure has

FIG. 9

realized a device with a high breakdown voltage and a low on-resistance (RON) over the limit of the material.").

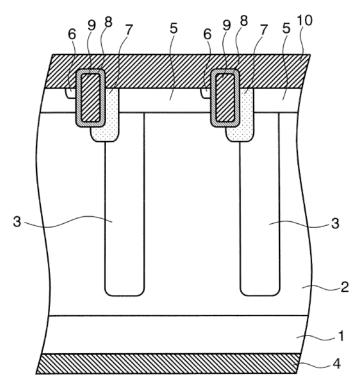

Gemäß der in der hier wiedergegebenen Fig. 9 handelt es sich bei dieser Struktur um einen vertikalen MOSFET mit einer parallelgeschalteten Diode. So wird der eigentliche MOSFET in Fig. 9 durch den n-dotierten Sourcebereich (*n-source region 6*), das p-dotierte Bodygebiet (*p-base region 5*) und den n-dotierten Driftbereich (*n-pillar region 2*) gebildet. Gesteuert wird er durch eine Gateelektrode (*gate electrode 9*), die sich in einem Graben befindet und durch einen Isolierfilm (*insulating film 8*), der auch das Gatedielektrikum bildet, isoliert wird. Parallel zu diesem MOSFET erstreckt sich eine Struktur bestehend aus dem p-dotierten Guardring (*guard ring 7*) und der p-Säule (*p-pillar region 3*). Sie bildet zum n-Bereich (*2*) einen pn-Übergang und stellt somit eine parallelgeschaltete Diode dar. Der pn-Übergang erstreckt sich entlang der Grenze der p-Säule (*3*) und des Guardrings (*7*) bis zum Boden des Grabens, in dem sich die Gateelektrode (*9*) befindet.

Damit offenbart Druckschrift D1 in Übereinstimmung mit dem Wortlaut des geltenden Anspruchs 1 nach Hauptantrag ein

- 1. Halbleiterbauelement (siehe Fig. 9),

- 1.1 das einen Halbleiterkörper (*Bezugszeichen 1 bis 7*) und wenigstens zwei Bauelementzellen (*siehe die Wiederholung der Struktur*), die in dem Halbleiterkörper integriert sind, aufweist, wobei jede Bauelementzelle aufweist:

- 1.2 ein Driftgebiet (*n-pillar region 2*),

- 1.3 ein Sourcegebiet (*n-source region 6*) und ein

- 1.4 Bodygebiet (*p-base region 5*), das zwischen dem Sourcegebiet (*6*) und dem Driftgebiet (*2*) angeordnet ist;

- 1.5 ein Diodengebiet (Gebiete 7 und 3) und

- 1.6 einen pn-Übergang zwischen dem Diodengebiet (7, 3) und dem Driftgebiet (2);

- 1.7 einen Graben mit einer ersten Seitenwand (*linke Seitenwand*), einer zweiten Seitenwand (*rechte Seitenwand*) gegenüber der ersten Seitenwand und einem Boden (*Unterseite*),

- 1.8 wobei das Bodygebiet (5) an die erste Seitenwand (*linke Seitenwand*) angrenzt, das Diodengebiet (7) an die zweite Seitenwand (*rechte Seitenwand*) angrenzt und der pn-Übergang an den Boden des Grabens angrenzt (*siehe den Verlauf des Gebiets 7, dessen Grenze an den Boden des Grabens angrenzt und auch den pn-Übergang ausbildet*);

- 1.9 eine Gateelektrode (*gate electrode 9*), die in dem Graben angeordnet ist und die durch ein Gatedielektrikum (*insulating film 8*) gegenüber dem Bodygebiet (*5*), dem Diodengebiet (*7, 3*) und dem Driftgebiet (*2*) isoliert ist (*vgl. Abs. [0061]: "FIG. 9 is a schematic cross section showing the structure of a MOSFET according to a sixth embodiment of the invention. Elements similar to those in the MOSFET shown in FIG. 1 are marked with the same reference numerals and not described in detail." und Abs. [0037]: "A trench groove is formed so as to extend from the n-source region 6 via the p-base region 5 to the n-pillar region 2, and a gate electrode 9 (control electrode) is formed via a gate insulating film 8."); und*

- 1.10 eine Sourceelektrode (source electrode 10), die an das Sourcegebiet (6) und das Diodengebiet (7) jeder Bauelementzelle elektrisch angeschlossen ist (vgl. Abs. [0038]: "A source electrode 10 (second main electrode) is formed on the p-base region 5, the n-source region 6, and the p-guard ring region 7, and electrically connected thereto."),

- 1.11 wobei die Diodengebiete (7, 3) der wenigstens zwei Bauelementzellen in einer lateralen Richtung des Halbleiterkörpers beabstandet sind und jeweils aufweisen:

- 1.11.1 ein erstes Diodengebiet (*p-pillar region 3*), das zumindest einen Teil des pn-Übergangs mit dem Driftgebiet (2) bildet, und

- 1.11.3 ein zweites Diodengebiet (*p-guard ring 7*), das höher dotiert ist als das erste Diodengebiet (3, *vgl. Abs. [0037]: "A p-base region 5 (third semiconductor region) is formed on the surface of the n-pillar region 2, and an n-source region 6 (fourth semiconductor region) is formed on the surface of the p-base region 5. A p- guard*

ring region 7 (fifth semiconductor region) having a higher concentration than the p-pillar region is formed on the surface of the p-pillar region 3"),

1.11.4 wobei das zweite Diodengebiet (7) ein unteres Ende aufweist und mit einem oberen Ende an die Sourceelektrode (10) angeschlossen ist.

Damit unterscheidet sich der Gegenstand des Anspruchs 1 von dem aus Druckschrift D1 dadurch, dass das niedriger dotierte erste Diodengebiet gemäß den Merkmalen 1.11.2 und 1.11.5 an den Graben ausschließlich am Boden angrenzt; und das untere Ende des zweiten Diodengebiets lateral umschließt, denn das erste Diodengebiet (3) des in Druckschrift D1 offenbarten Halbleiterbauelements grenzt an den Graben nicht an und umschließt auch das untere Ende des zweiten Diodengebiets (7) lateral nicht, da es einen Teil des unteren Endes des zweiten Diodengebiets (7) gegenüber dem Driftgebiet (2) freilässt. Der Gegenstand des Anspruchs 1 ist somit gegenüber dem in Druckschrift D1 offenbarten neu (§ 3 PatG).

Druckschrift D1 gibt auch keinerlei Anregung, auf Grund derer der Fachmann die Teilgebiete (7, 3) des Diodengebiets in ihrer Form oder Anordnung verändern würde, so dass der Gegenstand des Anspruchs 1 dem Fachmann durch Druckschrift D1 auch nicht nahegelegt wird (§ 4 PatG).

**4.2.** In der Stammakte wurde noch eine weitere Druckschrift, die Druckschrift D2 eingeführt, von der es im Erstbescheid der Prüfungsstelle ohne genauere Ausführungen heißt, dass auch sie den Gegenstand des zu diesem Zeitpunkt

FIG. 3

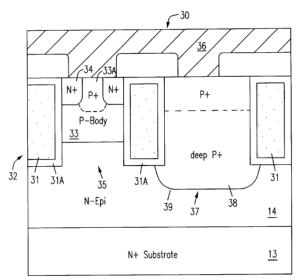

neuheitsschädlich vorwegnehme. Sie offenbart ebenfalls einen Graben-MOSFET,

zu dem eine Diode parallelgeschaltet ist (vgl. den Titel:

"Trench-gated power

MOSFET with protective

**Anspruchs**

geltenden

diode"). Von besonderem Interesse ist dabei die in der hier wiedergegebenen Fig. 3 gezeigte Ausführungsform. Bei dieser handelt es sich in Übereinstimmung mit dem Wortlaut des Anspruchs 1 um ein

- 1. Halbleiterbauelement,

- 1.1 das einen Halbleiterkörper und wenigstens zwei Bauelementzellen, die in dem Halbleiterkörper integriert sind, aufweist (vgl. Sp. 2, Z. 56 bis 59: "The MOSFET is formed as a plurality of cells which are defined by the gate trench. The cells may be of any shape. For example, the cells may be in the form of a square or hexagon or a series of parallel stripes or rectangles." und siehe Fig. 6 i.V.m. Sp. 5, Z. 9 bis 10: "FIG. 6 shows a top view of the MOSFET 30 shown in FIG. 3."), wobei jede Bauelementzelle aufweist:

- 1.2 ein Driftgebiet (N-Epi Bereich 14),

- 1.3 ein Sourcegebiet (N+ source region 34) und ein

- 1.4 Bodygebiet (*P-body region 33*), das zwischen dem Sourcegebiet (*34*) und dem Driftgebiet (*14*) angeordnet ist;

- 1.5 ein Diodengebiet (*cell 37, vgl. Sp. 4, Z. 28 bis 32: "In a neighboring cell 37 a protective deep P+ diffusion 38 is formed. Diffusion 38 forms a PN junction 39 with N-epitaxial layer 14. Metal layer 36 contacts protective diffusion 38, and thus PN junction 39 represents a diode which is connected in parallel with the channel of cell 35."*) und

- 1.6 einen pn-Übergang (*PN junction 39*) zwischen dem Diodengebiet (*37*) und dem Driftgebiet (*14*);

- 1.7 einen Graben mit einer ersten Seitenwand (*linke Wand des mittleren Grabens mit Gateelektrode 31*), einer zweiten Seitenwand (*rechte Wand des Grabens*) gegenüber der ersten Seitenwand und einem Boden (*Unterseite des Grabens*),

- 1.8 wobei das Bodygebiet (33) an die erste Seitenwand (*linke Wand*) angrenzt, das Diodengebiet (37) an die zweite Seitenwand (*rechte Wand*) angrenzt und der pn-Übergang (39) an den Boden des Grabens angrenzt;

- 1.9 eine Gateelektrode (*gate 31*), die in dem Graben angeordnet ist und die durch ein Gatedielektrikum (*oxide layer 31A*) gegenüber dem Bodygebiet (*33*), dem Diodengebiet (*37*) und dem Driftgebiet (*14*) isoliert ist; und

- 1.10 eine Sourceelektrode (*metal layer 36*), die an das Sourcegebiet (*34*) und das Diodengebiet (*37*) jeder Bauelementzelle elektrisch angeschlossen ist (*vgl. Sp. 4, Z. 19 bis 21: "A metal layer 36 makes contact with and forms a short between P-body region 33 and N+ source region 34." und die bereits zitierte Sp. 4, Z. 30 bis 32),*

- 1.11 wobei die Diodengebiete (37) der wenigstens zwei Bauelementzellen in einer lateralen Richtung des Halbleiterkörpers beabstandet sind (siehe die beabstandeten Positionen der P+-Gebiete in Fig. 6) und jeweils aufweisen:

- 1.11.1 ein erstes Diodengebiet (*Teil des Gebiets 38 unter der gestrichelten Linie*), das zumindest einen Teil des pn-Übergangs (*39*) mit dem Driftgebiet (*14*) bildet und 1.11.2' an den Graben am Boden angrenzt; und

- 1.11.3 ein zweites Diodengebiet (*Teil des Gebiets 38 über der gestrichelten Linie*), das höher dotiert ist als das erste Diodengebiet,

- 1.11.4 wobei das zweite Diodengebiet ein unteres Ende (*gestrichelte Linie*) aufweist und mit einem oberen Ende an die Sourceelektrode (*36*) angeschlossen ist.

Das Merkmal, dass das zweite Diodengebiet höher dotiert ist als das erste Diodengebiet, wird zwar nicht explizit in Druckschrift D2 ausgeführt, ergibt sich aber aus dem Herstellungsprozess. So wird zunächst eine p-Dotierung mit einer Dosis von 1×10<sup>14</sup> bis 7×10<sup>15</sup> cm<sup>-2</sup> durch eine dünne Oxidschicht mit einer Energie von 60 bis 100 keV implantiert. Dadurch entsteht eine Dotierung mit einem vergleichsweise breiten Maximum in der Tiefe und einer Ausdehnung bis an die Oberfläche (siehe Fig. 14A i. V. m. dem Text Sp. 7, Z. 27 bis 33: "A thick oxide layer 140 is grown, masked and etched, and a thin oxide layer 141 is grown on the top surface of the structure where deep P+ region 38 is to be formed. Deep P+ region 38 is then implanted through thin oxide layer 141 at a dose of 1×10<sup>14</sup> to 7×10<sup>15</sup> cm<sup>-2</sup> and an energy of 60-100 keV. The resulting structure is illustrated in FIG. 14A. Oxide layers 140 and 141 are then removed."). Der Teil des flachen Abfalls des Dotierungsprofils

in Richtung der Oberfläche, der sich in der dünnen Oxidschicht befindet, wird dabei mit der Oxidschicht entfernt.

In einem späteren Schritt (siehe Fig. 14E) wird in die tiefe p-Dotierung nochmals eine p-Dotierung implantiert, diesmal mit einer Dosis von 1x10<sup>13</sup> bis 5x10<sup>14</sup> cm<sup>-2</sup> und einer Energie von 20 bis 80 keV ohne Oxidschicht (vgl. Sp. 7, Z. 62 bis Sp. 8, Z. 6: "Following the formation of the N+ source region 38, a new mask is formed and the shallow P+ region 33A that is used to contact the P-body is introduced by ion implantation at a dose of  $1 \times 10^{13}$  to  $5 \times 10^{14}$  cm<sup>-2</sup> at 20-80 keV. Alternatively, as shown in FIG. 14E, shallow P+ region 33A can be formed by implanting P-type dopant through the same mask that is used in forming the contact holes for the N+ source region/P+ contact region and the deep P+ region. Although with this technique some of the P-type dopant is implanted into N+ source region 34, the level of P-type doping is not sufficient to significantly affect the concentration of N-type ions in the N+ source region."). Bereits der Überlapp der Dotierstoffdosen zeigt, dass es Ausführungsformen gibt, bei denen der Bereich nahe der Oberfläche höher dotiert ist als der Bereich weiter in der Tiefe, zumal sich zudem die Dotierstoffmenge beim tieferliegenden Bereich über ein größeres Volumen verteilt als bei der flacheren Dotierung nahe der Oberfläche und letztere zusätzlich zur vorhandenen tieferen Dotierung eingebracht wird.

Damit unterscheidet sich das Halbleiterbauelement nach Anspruch 1 von dem in Druckschrift D2 offenbarten dadurch, dass das erste Diodengebiet ausschließlich an den Boden des Grabens grenzt und nicht, wie in Fig. 3 der Druckschrift D2 offenbart, auch an die zweite Seitenwand. Zudem umschließt gemäß Merkmal 1.11.5 das erste Diodengebiet das untere Ende des zweiten Diodengebiets lateral, während es bei dem in Druckschrift D2 gezeigten Ausführungsbeispiel lediglich die Unterseite des zweiten Diodengebiets bedeckt. Ein Umschließen ist nicht möglich, da der Übergang zwischen beiden Gebieten im Bereich zwischen den Gräben liegt, die die Diodengebiete seitlich begrenzen.

Der Gegenstand des Anspruchs 1 ist somit neu (§ 3 PatG) gegenüber der Lehre der Druckschrift D2 und kann durch diese auch nicht nahegelegt werden. Da keine der beiden Druckschriften ein erstes Diodengebiet offenbart, das an den Graben ausschließlich am Boden angrenzt, kann auch eine Zusammenschau der beiden Druckschriften D1 und D2 nicht zum mit Anspruch 1 beanspruchten Gegenstand führen, weshalb das Halbleiterbauelement nach Anspruch 1 demnach auch auf einer erfinderischen Tätigkeit des Fachmanns (§ 4 PatG) beruht, so dass es patentfähig ist (§ 1 Abs. 1 PatG).

- **4.3.** Das Verfahren des Anspruchs 9 ist aus denselben Gründen wie Anspruch 1 patentfähig, da es ebenfalls die Merkmale aufweist (Merkmale 9.3.4 und 9.3.5), die die Patentfähigkeit des Gegenstands des Anspruchs 1 begründen. Dagegen können die die Herstellung einer Sourceelektrode betreffenden Merkmale 9.5 bis 9.7 die Patentfähigkeit nicht begründen, da sie bereits aus Druckschrift D2 bekannt sind (siehe Fig. 3 i. V. m. dem Text Sp. 8, Z. 7 bis 15: "A thin oxide layer is thermally grown. Borophosphosilicate glass (BPSG) is then deposited on the surface of the structure. The BPSG is momentarily heated to around 850° to 950° C. to flow smoothly and flatten the surface topology of the die. Contact holes are etched in the oxide and BPSG layers, and metal layer 36 is deposited, forming contacts with the source and body regions and the deep P+ region through the contact holes. This yields MOSFET 30 shown in FIG. 3.").

- **5.** An die Patentansprüche 1 und 9 können sich die Unteransprüche 2 bis 8 bzw. 10 bis 13 anschließen, da sie vorteilhafte Weiterbildungen des beanspruchten Halbleiterbauelements bzw. Verfahren zum Herstellen eines solchen, welche nicht platt selbstverständlich sind, darstellen.

- **6.** In der in der mündlichen Verhandlung am 30. Juni 2020 angepassten Beschreibung ist der Stand der Technik, von dem die Erfindung ausgeht, angegeben und die Erfindung anhand der am 23. Oktober 2019 im Deutschen Patent- und Markenamt eingegangenen Zeichnung ausreichend erläutert.

**7.** Bei dieser Sachlage war der angefochtene Beschluss aufzuheben und das Patent wie beantragt zu erteilen.

III.

## Rechtsmittelbelehrung

Gegen diesen Beschluss steht der Anmelderin das Rechtsmittel der Rechtsbeschwerde zu. Da der Senat die Rechtsbeschwerde nicht zugelassen hat, ist sie nur statthaft, wenn einer der nachfolgenden Verfahrensmängel gerügt wird, nämlich

- 1. dass das beschließende Gericht nicht vorschriftsmäßig besetzt war,

- 2. dass bei dem Beschluss ein Richter mitgewirkt hat, der von der Ausübung des Richteramtes kraft Gesetzes ausgeschlossen oder wegen Besorgnis der Befangenheit mit Erfolg abgelehnt war,

- 3. dass einem Beteiligten das rechtliche Gehör versagt war,

- 4. dass ein Beteiligter im Verfahren nicht nach Vorschrift des Gesetzes vertreten war, sofern er nicht der Führung des Verfahrens ausdrücklich oder stillschweigend zugestimmt hat,

- 5. dass der Beschluss aufgrund einer mündlichen Verhandlung ergangen ist, bei der die Vorschriften über die Öffentlichkeit des Verfahrens verletzt worden sind, oder

- 6. dass der Beschluss nicht mit Gründen versehen ist.

Die Rechtsbeschwerde ist **innerhalb eines Monats** nach Zustellung des Beschlusses

schriftlich durch einen beim Bundesgerichtshof zugelassenen Rechtsanwalt als Bevollmächtigten beim Bundesgerichtshof, Herrenstr. 45 a, 76133 Karlsruhe, einzureichen oder

durch einen beim Bundesgerichtshof zugelassenen Rechtsanwalt als Bevollmächtigten in elektronischer Form. Zur Entgegennahme elektronischer Dokumente ist die elektronische Poststelle des Bundesgerichtshofs bestimmt. Die elektronische Poststelle des Bundesgerichtshofs ist über die auf der Internetseite www.bundesgerichtshof.de/erv.html bezeichneten Kommunikationswege erreichbar. Die Einreichung erfolgt durch die Übertragung des elektronischen Dokuments in die elektronische Poststelle. Elektronische Dokumente sind mit einer elektronischen oder mit qualifizierten Signatur einer fortgeschrittenen elektronischen Signatur zu versehen.

Dr. Strößner Dr. Zebisch Dr. Himmelmann Dr. Kapels

prö